Voulez-vous savoir comment obtenir un travail de conception d'électronique de vaisseau spatial? J'ai récemment reçu une offre d'interview pour le poste de designer FPGA pour Blue Origin (voir ci-dessus). Personnellement, je n'ai pas besoin d'un tel poste (j'ai déjà un poste de concepteur ASIC dans une autre entreprise), mais j'ai noté que les exigences techniques pour les candidats à Blue Origin coïncident exactement avec le contenu du séminaire pour les écoliers et les étudiants juniors, qui se tiendra du 15 au 17 septembre au salon ChipEXPO à Skolkovo , avec le soutien de RUSNANO. Bien que, bien sûr, lors du séminaire, nous n'aborderons les technologies Verilog et FPGA qu'au niveau très initial: concepts de base et exemples simples, mais déjà intéressants. Pour décrocher ensuite un emploi chez Blue Origin, il vous faudra encore quelques années d'études et de travail.

En raison du coronavirus, le séminaire sera éloigné, de sorte que non seulement les écoliers et les étudiants de Moscou, mais également toute la Russie, l'Ukraine, le Kazakhstan, la Californie et d'autres pays et régions pourront y participer. Des conférenciers et ingénieurs de MIET, HSE MIEM, MIPT, Université polytechnique de Tchernigov, Université de Samara, IVA Technologies et fpga-systems.ru dirigeront physiquement des conférences et assisteront à distance les participants .

Pour participer en premier, avant même le séminaire, vous devez suivre trois parties d'un cours théorique de RUSNANO, sous le titre général "Comment fonctionnent les créateurs de nanopuces intelligentes": "Du transistor au microcircuit", "Côté logique du circuit numérique", "Côté physique du circuit numérique". Ce cours est essentiel pour que vous compreniez ce que vous faites pendant l'atelier. Après avoir reçu un certificat d'achèvement du cours théorique en ligne, vous pouvez vous rendre au bureau de RUSNANO à Moscou et recevoir des frais gratuits pour un séminaire pratique (s'ils restent, les écoliers ont la priorité). Avec cette carte, vous pouvez travailler à la maison, avant, pendant et après le séminaire de Skolkovo.

Comment être payé, préparer le séminaire et ce qu'il y aura dessus:

Vous pouvez trouver des instructions sur la façon d'obtenir des frais sur le site Web de STEMford . STEMford est un programme éducatif pour les écoliers d' eNano , une filiale de la Fondation RUSNANO pour les programmes éducatifs d'infrastructure. Voici leur bureau à visiter:

Avant le laboratoire, vous devrez installer Intel Quartus Prime Lite Edition sur votre ordinateur. Les instructions sur la façon de procéder se trouvent dans le fragment gratuit du livre "Synthèse numérique: un cours pratique" édité par A. Yu. Romanov, Yu. V. Panchul. DMK Press, 2020.

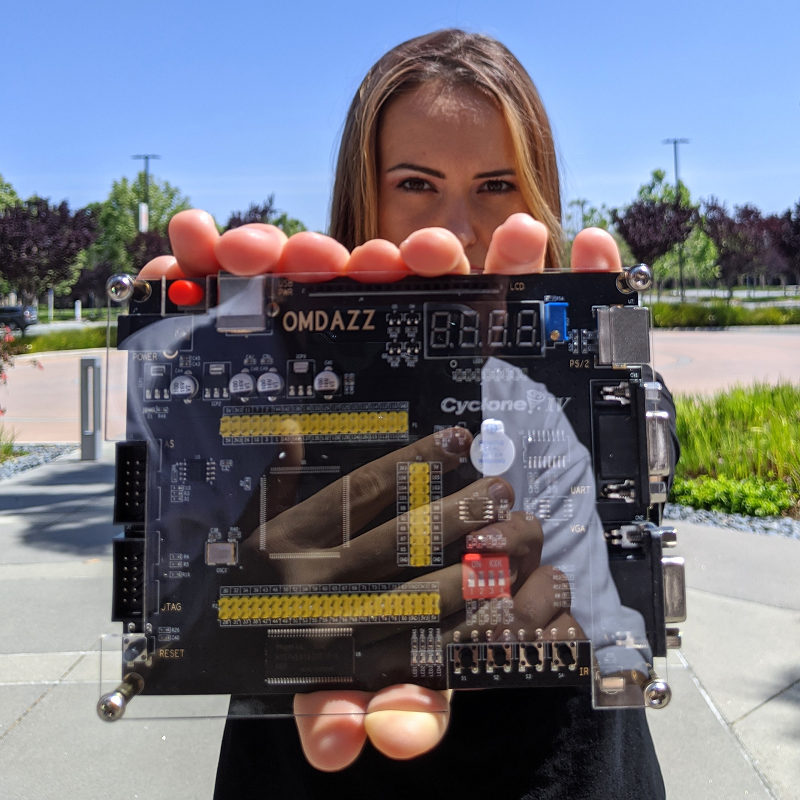

En général, "Digital Synthesis" est un livre utile pour un séminaire, il décrit des exercices qui seront présentés avec quelques variantes lors du séminaire, bien que par exemple, au lieu du processeur pédagogique schoolMIPS, unschoolRISCV : À la fin du livre Digital Synthesis , il y a une interview plutôt amusante avec un couple de jeunes mariés Vladislav et Elena Sharshin, qui, avec leur collègue Andrei Papushin, Intel a amené en Californie pour la victoire d'argent au concours InnovateFPGA: Voici l'une des cartes qui sera utilisée lors du séminaire. S'il n'y a pas assez de planches pour vous, ou si vous n'êtes pas étudiant, vous pouvez commander une planche sur AliExpress et ailleurs: 1 , 2 , 3 , 4 : Que se passera-t-il lors du séminaire? Voici les parties du programme :

15 . .

: , « » ().

15.00. , .

15.15-15.30. -: Apple iPhone: .

, . , .

15.30-16.00. : Verilog. /FPGA Intel Quartus Prime Lite Edition. .

16.00-16.30.

///-, , c .

16.30-17.00. .

17.00-17.30. : , .

17.30-18.00. .

18.00-19.00. ZEOWAA OMDAZZ Intel FPGA Cyclone IV: : ( ). Terasic DE10-Lite Intel FPGA MAX10: : ( ).

19.00-21.00. , : , , ,

.

Le premier jour est basé sur l'expérience de l'organisation du séminaire de l'année dernière à Moscou, qui est décrit dans un article sur Habré : Le

deuxième jour est basé sur l'expérience de la tenue d'une école d'été à Zelenograd l'année dernière et de séminaires à Samara:

16 . .

: , , , .

15.00-15.15. -: : , .

.

15.15-15.30. : VGA.

.

15.30-16.00. .

16.00-16.30. . Digilent Basys3 Xilinx FPGA Artix-7. .

, fpga-systems.ru.

16.30-17.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

17.00-17.30. : Linear Feedback Shift Registers (LFSR) . Verilog VHDL LFSR . LFSR VGA .

, .

17.30-18.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

18.00-19.00. .

.

18.00-21.00. , . .

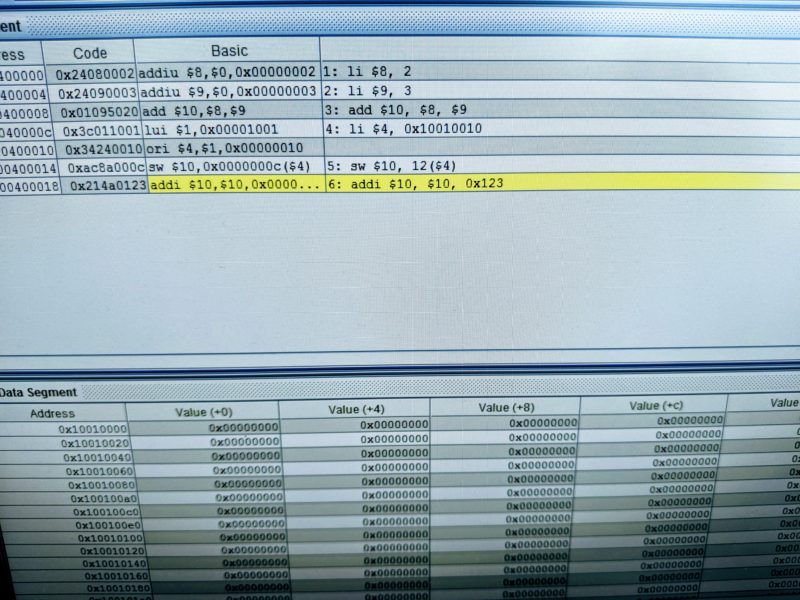

Le troisième jour sera basé sur l'expérience du programme éducatif sur les processeurs de Stanislav Zhelnio et Alexander Romanov . Seulement avant qu'ils aient développé et utilisé le processeur d'apprentissage schoolMIPS, et maintenant nous utiliserons schoolRISCV. L'architecture RISC-V est très similaire à MIPS et aux autres architectures RISC (SPARC, ARM, POWER, etc.), mais débarrassée de leurs béquilles, ce qui avait du sens sur des processeurs simples, mais interfère avec des processeurs complexes (enregistrer les fenêtres dans SPARC, qui n'ont aucun sens dans les logiciels avec une grande pile; les créneaux de délai de branchement dans MIPS jusqu'à Rev6, qui conviennent à un simple pipeline statique avec récupération séquentielle d'instructions, mais se transforment en casse-tête dans un pipeline dynamique, etc.).

Puisqu'en Russie, il y a au moins trois entreprises qui conçoivent des processeurs sur l'architecture RISC-V, et c'est un bon candidat pour un futur processeur haut de gamme intégré russe et peut-être même de bureau et de serveur, et puisque RISC-V remplace en toute confiance MIPS en tant que chevaux pour l'expérimentation architecturale et microarchitecturale dans les universités du monde, alors il vaut mieux que les écoliers enseignent là-dessus.

17 . .

— , ..., . .. (), « » ( ).

15.00-15.15. -: ENIAC , IBM/360 Cray-1 Intel, ARM RISC-V: , .

.

15.15-16.30. : . RISC-V .

, - .

16.30-17.30. : . schoolRISCV, . .

, IVA Technologies.

17.30-17.30. . .

.

17h30-18h00. Conférence de clôture: Les prochaines étapes de la maîtrise de la conception de circuits numériques et de l'application de ces connaissances à la conception de systèmes embarqués et aux accélérateurs de calcul d'intelligence artificielle.

Alexander Yurievich Romanov.

18.00-21.00. Exercices supplémentaires et projets individuels d'étudiants sur le changement du processeur et son intégration avec des périphériques. Avec l'aide d'étudiants de premier cycle et des cycles supérieurs en microélectronique des universités participantes.

Voici Stanislav Zhelnio enseignant aux écoliers l'été dernier à Zelenograd:

Rendez-vous à un séminaire au ChipEXPO virtuel à Skolkovo! Nous essaierons d'y organiser une partie de l'événement et de vivre, avec l'aide d'enseignants de MIET, HSE MIEM et MIPT, mais si le virus ne le permet pas, nous le conduirons de manière distribuée.