Toutes les unités centrales de n'importe quel ordinateur, qu'il s'agisse d'un ordinateur portable bon marché ou d'un serveur pour des millions de dollars, ont un appareil appelé cache. Et avec une probabilité très élevée, il a plusieurs niveaux.

C'est probablement important, sinon pourquoi l'installer? Mais que fait le cache et pourquoi a-t-il des niveaux différents? Et que signifie «associatif à 12 voies»?

Qu'est-ce que le cache?

TL; DR: Il s'agit d'une mémoire petite mais très rapide située à proximité des blocs logiques du CPU.

Cependant, on peut bien sûr en apprendre beaucoup plus sur le cache ...

Commençons par un système de stockage magique imaginaire: il est infiniment rapide, peut gérer un nombre infini de transferts de données en même temps, et fournit toujours un stockage fiable et sécurisé. Bien sûr, rien de tel n'existe à proximité, mais s'il en était ainsi, la structure du processeur serait beaucoup plus simple.

Les processeurs n'auraient alors besoin que de blocs logiques pour l'addition, la multiplication, etc., ainsi que d'un système de contrôle de transmission de données, car notre système de stockage théorique est capable de transmettre et de recevoir instantanément tous les nombres nécessaires; aucun bloc logique ne doit rester inactif en attendant que les données soient transférées.

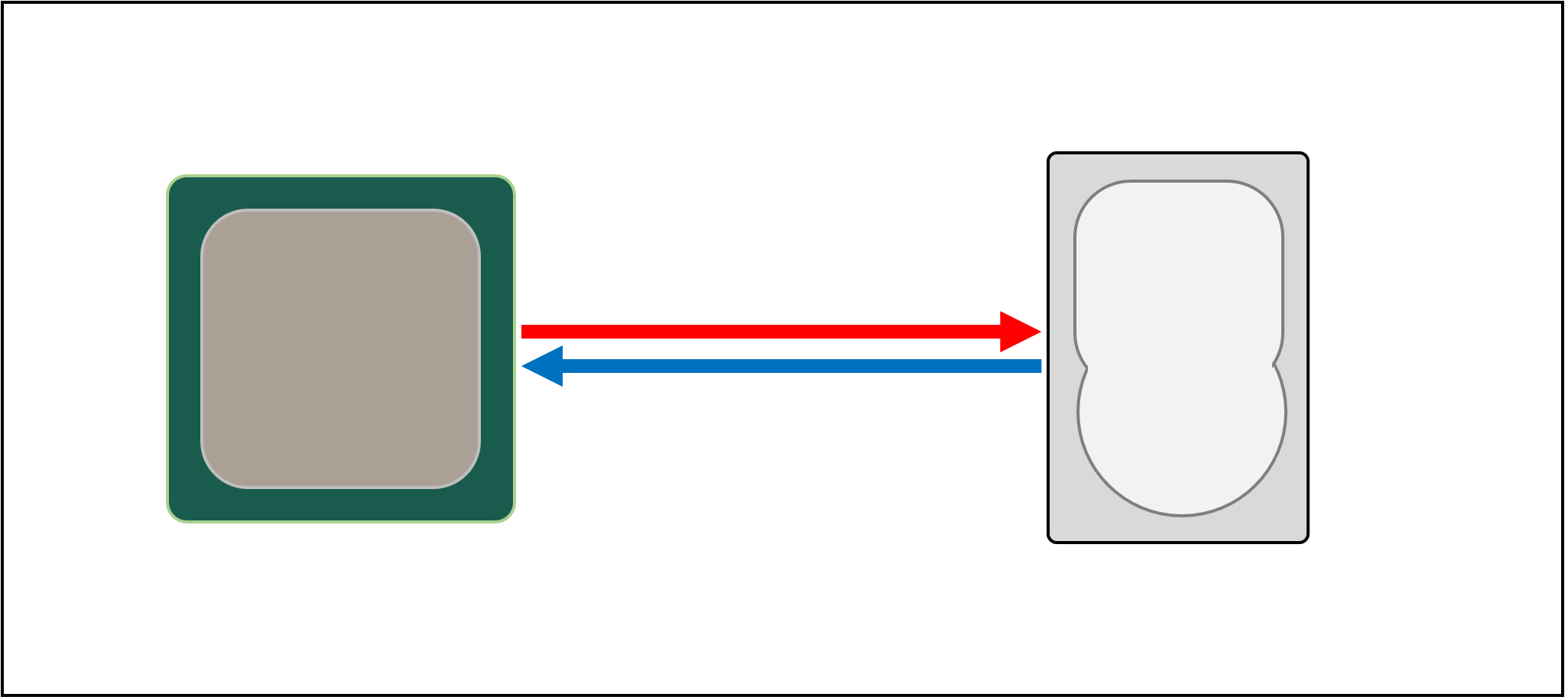

Mais, comme nous le savons, une telle technologie de stockage magique n'existe pas. Au lieu de cela, nous avons des disques durs ou des disques SSD, et même les meilleurs d'entre eux sont bien en deçà des capacités de traitement requises d'un processeur moderne.

Le grand T'Fon du stockage

La raison en est que les processeurs modernes sont incroyablement rapides - ils n'ont besoin que d'un cycle d'horloge pour ajouter deux entiers 64 bits; si le processeur fonctionne à 4 GHz, ce n'est que 0,0000000000025 secondes, soit un quart de nanoseconde.

Dans le même temps, un disque dur en rotation prend des milliers de nanosecondes juste pour trouver des données sur les disques, sans parler de leur transfert, et les disques SSD prennent des dizaines ou des centaines de nanosecondes.

De toute évidence, ces lecteurs ne peuvent pas être construits à l' intérieurprocesseurs, il y aura donc une séparation physique entre eux. Par conséquent, du temps est ajouté pour déplacer les données, ce qui aggrave la situation.

Hélas, c'est le grand A'Tuin du stockage de données

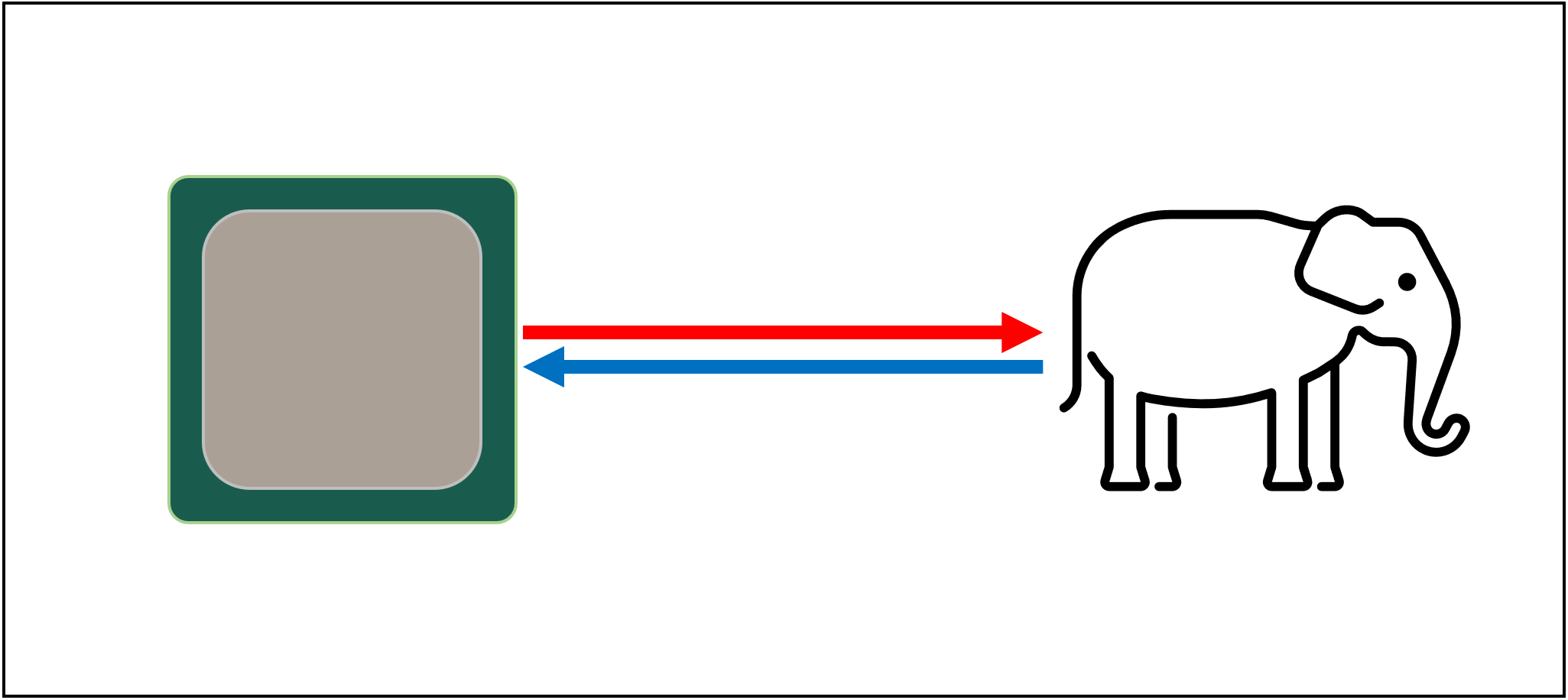

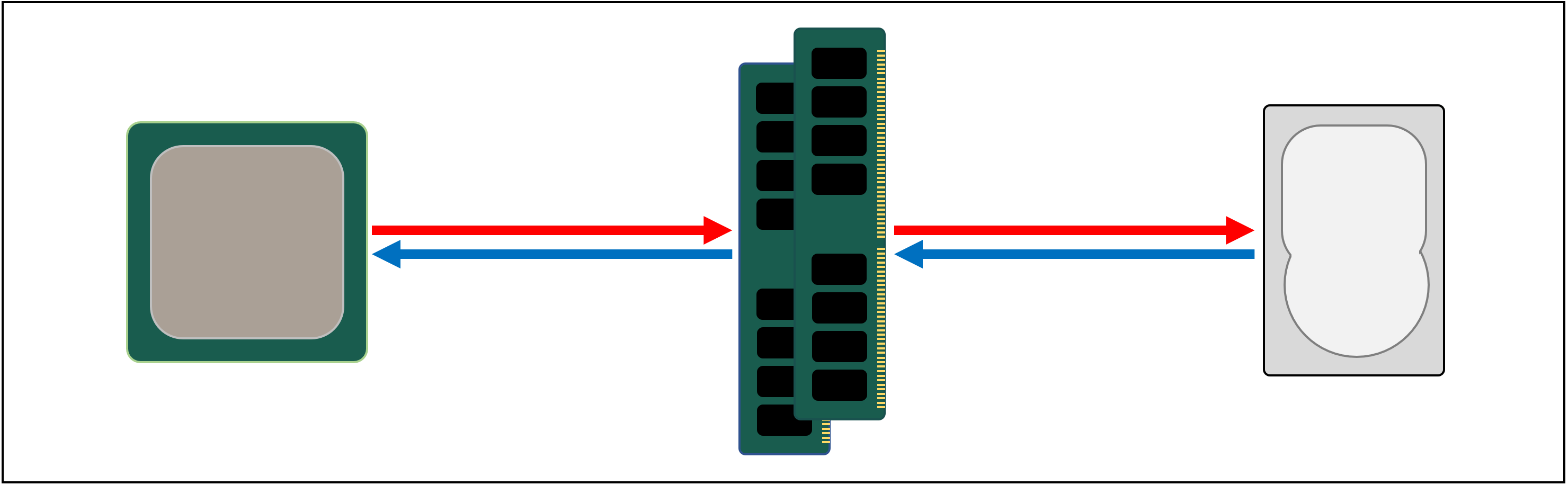

C'est pourquoi nous avons besoin d'un autre système de stockage situé entre le processeur et le disque principal. Il doit être plus rapide qu'un périphérique de stockage, capable de gérer plusieurs transferts de données simultanément et être beaucoup plus proche du processeur.

Eh bien, nous avons déjà un tel système, et il s'appelle RAM ; il est présent dans chaque ordinateur et effectue exactement cette tâche.

Presque tous ces stockages sont du type DRAM ( mémoire vive dynamique) ; ils sont capables de transférer des données beaucoup plus rapidement que n'importe quel périphérique de stockage.

Cependant, malgré son énorme vitesse, la DRAM n'est pas capable de stocker de telles quantités de données.

Certaines des plus grandes puces de mémoire DDR4 développées par Micron stockent 32 Go, soit 4 Go de données; les plus gros disques durs peuvent stocker 4 000 fois plus.

Ainsi, bien que nous ayons augmenté la vitesse de notre réseau de données, nous aurons besoin de systèmes supplémentaires (matériel et logiciel) pour déterminer quelles données doivent être stockées dans une quantité limitée de DRAM, prêtes à être traitées par le processeur.

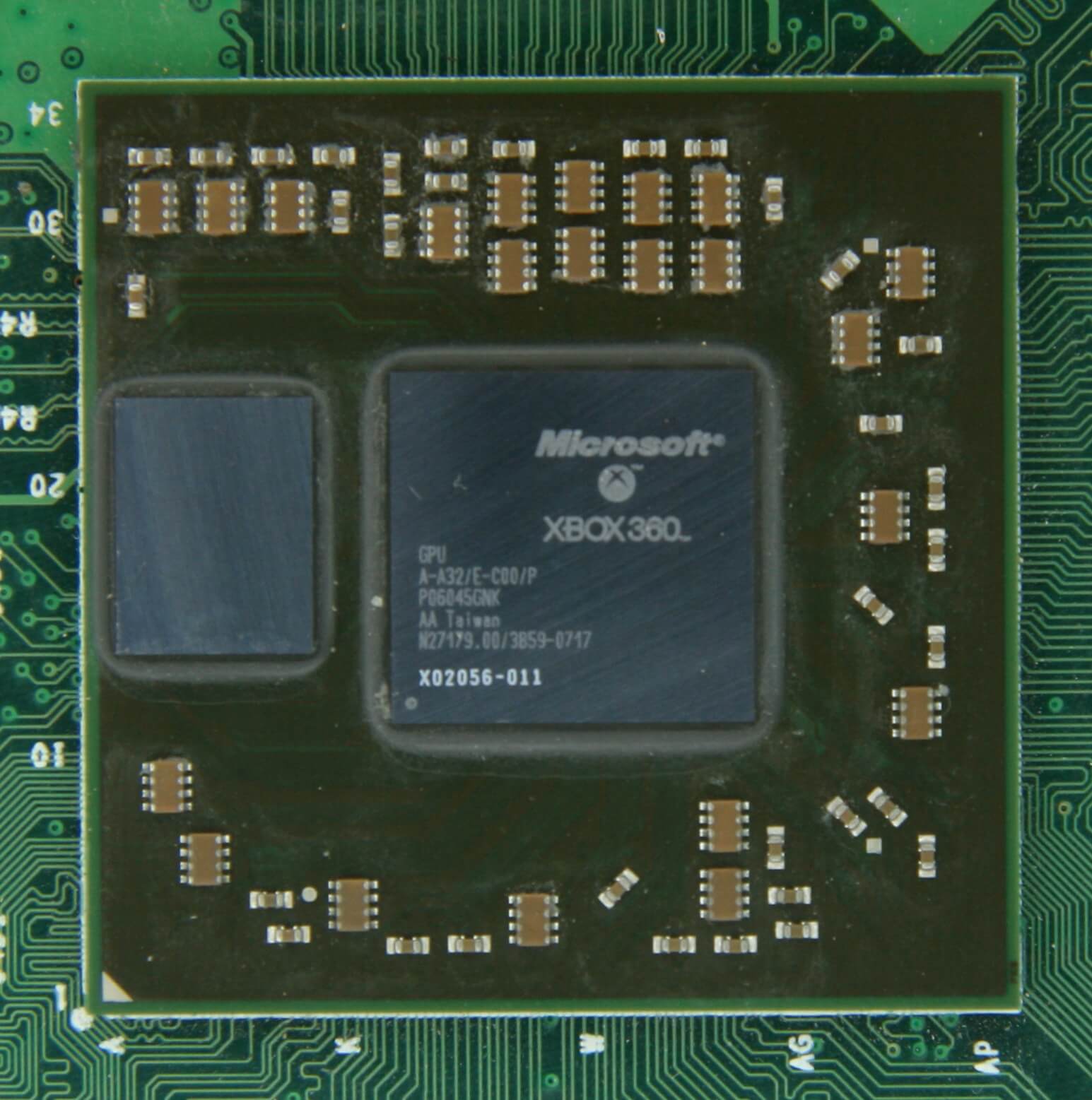

La DRAM peut être fabriquée dans un boîtier de puce (c'est ce qu'on appelle la DRAM intégrée). Cependant, les processeurs sont assez petits, ils ne peuvent donc pas contenir beaucoup de mémoire.

10 Mo de DRAM à gauche du GPU Xbox 360. Source: CPU Grave Yard

La grande majorité de la DRAM est située à proximité immédiate du processeur, connectée à la carte mère, et est toujours le composant le plus proche du processeur. Cependant, cette mémoire n'est toujours pas assez rapide ... La

DRAM met environ 100 nanosecondes pour trouver des données, mais au moins elle est capable de transférer des milliards de bits par seconde. Il semble que nous ayons besoin d'un autre étage de mémoire qui puisse être placé entre les blocs CPU et DRAM.

L'étage restant apparaît sur la scène: SRAM ( mémoire vive statique). La DRAM utilise des condensateurs microscopiques pour stocker les données sous forme de charge électrique, tandis que la SRAM utilise des transistors pour la même tâche, qui fonctionnent à la même vitesse que les blocs logiques du processeur (environ 10 fois plus rapide que la DRAM).

Bien sûr, SRAM a un inconvénient, et encore une fois, il a à voir avec l'espace.

La mémoire transistor occupe beaucoup plus d'espace que la DRAM: dans la même taille qu'une puce DDR4 de 4 Go, vous pouvez obtenir moins de 100 Mo de SRAM. Mais comme il est fabriqué selon le même processus de fabrication que le CPU, la SRAM peut être intégrée directement à l'intérieur du processeur, au plus près des blocs logiques.

À chaque étape supplémentaire, nous augmentons la vitesse des données transférées au détriment du volume stocké. Nous pouvons continuer et ajouter de nouvelles étapes, qui seront plus rapides, mais plus petites.

Et donc nous sommes arrivés à une définition plus stricteconcepts de cache: une collection de SRAM situées à l'intérieur du processeur; ils optimisent l'utilisation du processeur en transférant et en stockant les données à des vitesses très élevées. Êtes-vous satisfait de cette définition? Génial, car les choses vont devenir beaucoup plus compliquées à partir de maintenant!

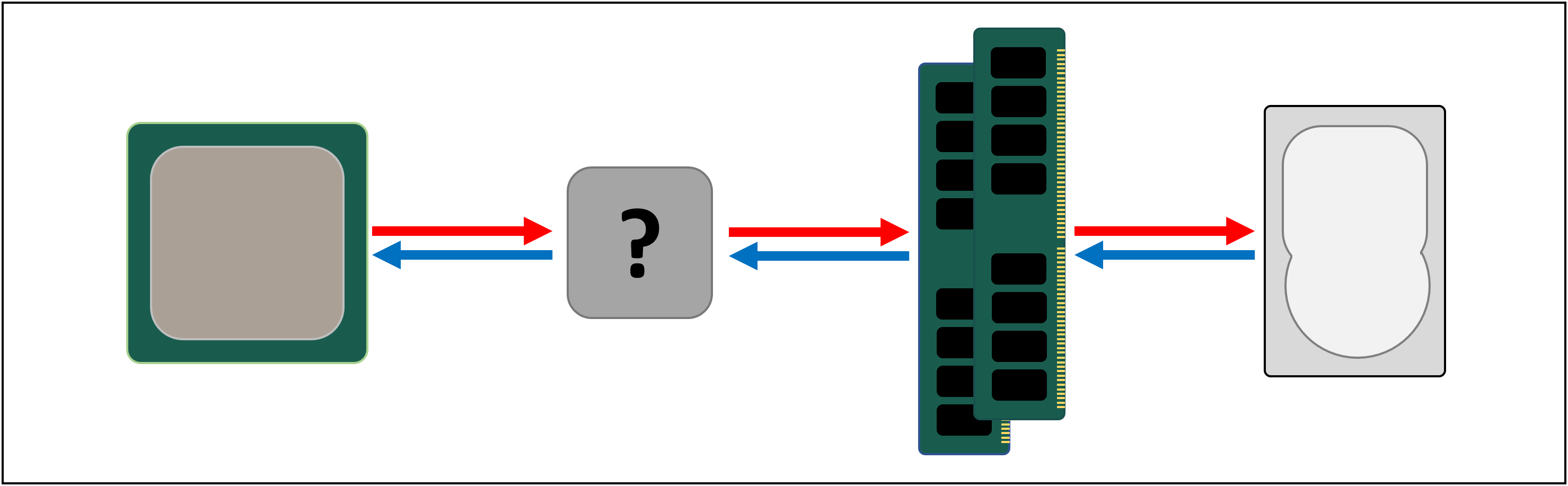

Espèces: parking à plusieurs niveaux

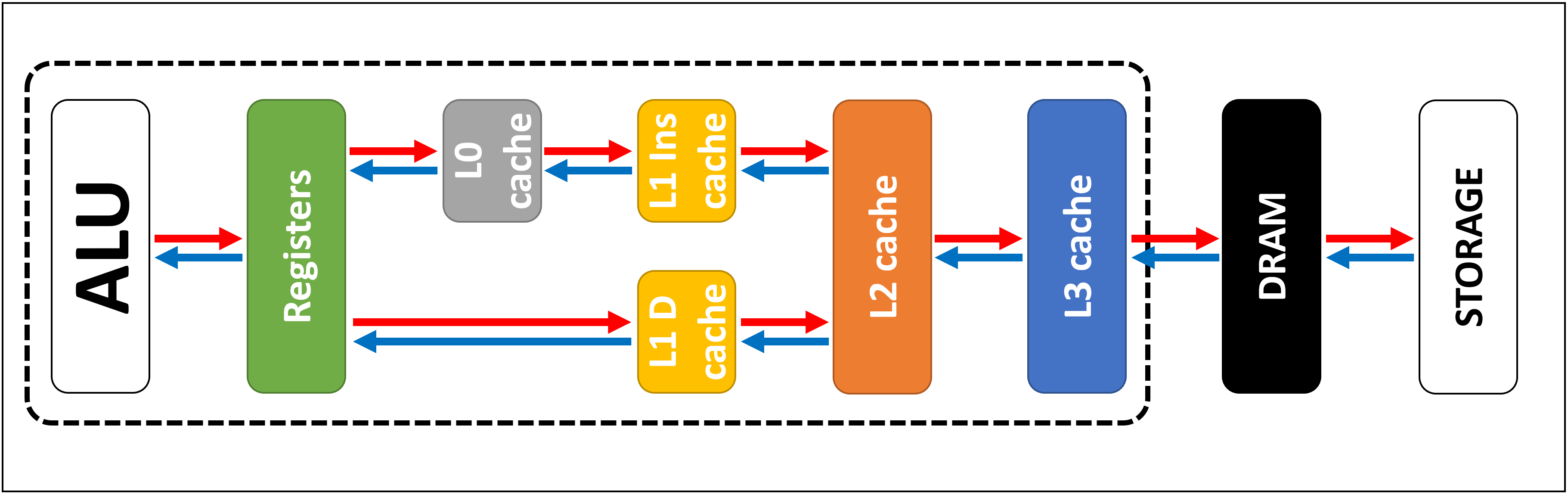

Comme nous l'avons dit ci-dessus, le cache est nécessaire car nous n'avons pas de système de stockage magique capable de gérer la consommation de données des blocs logiques du processeur. Les processeurs et GPU modernes contiennent de nombreuses SRAM, organisées dans une hiérarchie à l'intérieur - une séquence de caches avec la structure suivante:

Dans l'image ci-dessus, le processeur (CPU) est indiqué par un rectangle en pointillé. Sur la gauche se trouvent les ALU (unités arithmétiques et logiques); ce sont des structures qui effectuent des opérations mathématiques. Bien que n'étant pas strictement un cache, le niveau de mémoire le plus proche de l'ALU est les registres (ils sont classés dans un fichier de registre ).

Chacun d'eux stocke un nombre, par exemple, un entier de 64 bits; la valeur elle-même peut être un élément de certaines données, un code d'une instruction spécifique ou une adresse mémoire de certaines autres données.

Le fichier de registre dans les processeurs de bureau est assez petit, par exemple, dans chacun des cœurs Intel Core i9-9900Kil existe deux banques de ces fichiers, et celle pour les entiers ne contient que 180 entiers 64 bits. Un autre fichier de registre pour les vecteurs (petits tableaux de nombres) contient 168 éléments de 256 bits. Autrement dit, le fichier de registre total pour chaque cœur est légèrement inférieur à 7 Ko. À titre de comparaison, le fichier de registre Nvidia GeForce RTX 2080 Ti pour les multiprocesseurs en streaming (comme les GPU appellent les analogues de cœur de processeur) a une taille de 256 Ko.

Les registres, comme le cache, sont des SRAM, mais leur vitesse ne dépasse pas la vitesse des ALU qu'ils servent; ils transfèrent des données en un cycle d'horloge. Mais ils ne sont pas conçus pour stocker de grandes quantités de données (un seul élément), il y a donc toujours des blocs de mémoire plus gros à côté d'eux: c'est le cache de premier niveau (niveau 1).

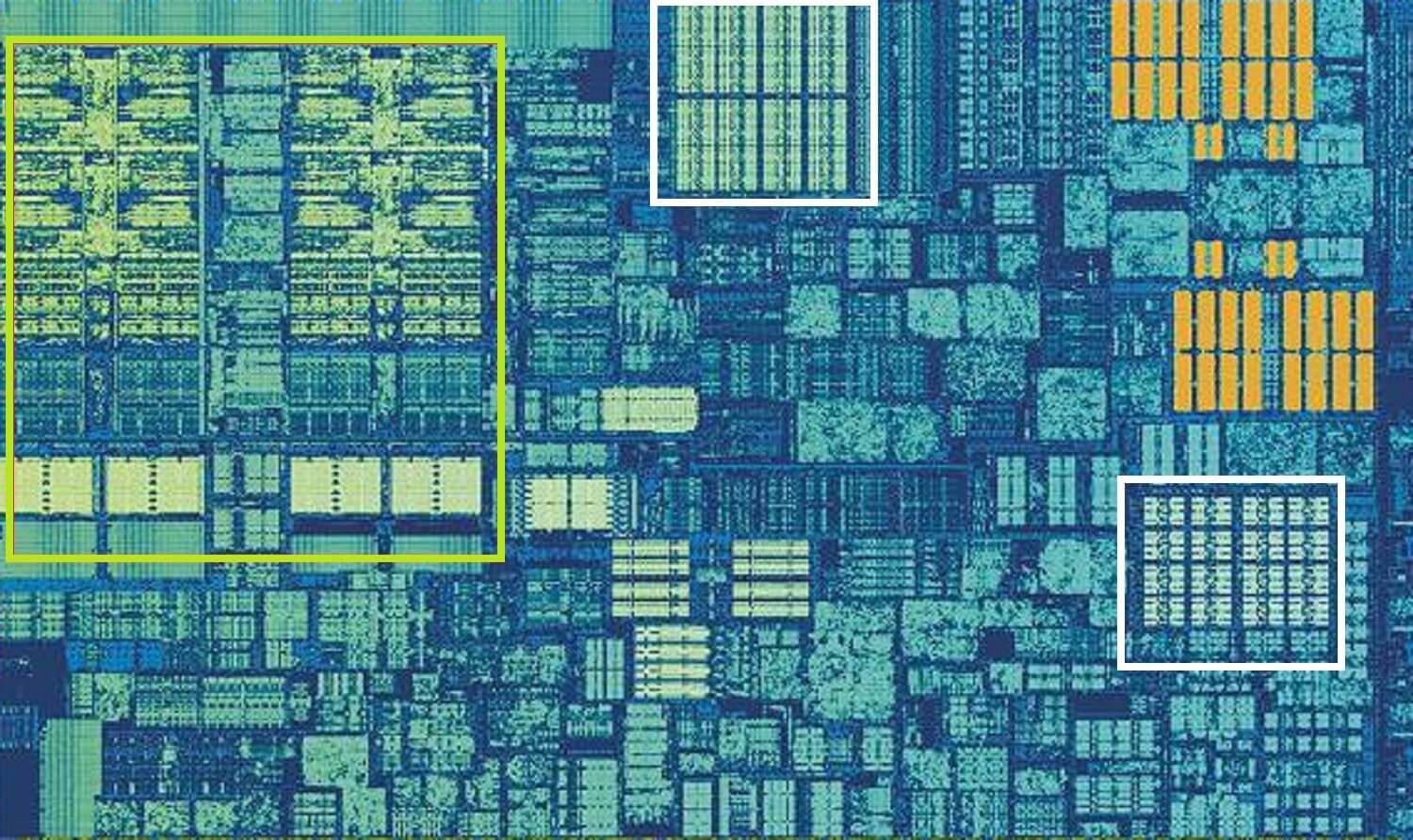

Un cœur de processeur Intel Skylake. Source: Wikichip

L'image ci-dessus est une vue agrandie de l'un des cœurs du processeur de bureau Intel Skylake .

Les fichiers ALU et registre sont situés sur la gauche et sont entourés d'un cadre vert. En haut de la photo, le cache de données de niveau 1 est indiqué en blanc. Il ne contient pas beaucoup d'informations, seulement 32 Ko, mais comme les registres, il est situé très près des blocs logiques et fonctionne à la même vitesse qu'eux.

Un autre rectangle blanc sur la droite montre le cache d'instructions de niveau 1, également d'une taille de 32 Ko. Comme son nom l'indique, il stocke diverses commandes prêtes à être divisées en micro-opérations plus petites .(généralement désigné par μops) que les ALU doivent exécuter. Il existe également un cache pour eux, qui peut être classé au niveau 0, car il est plus petit (ne contient que 1 500 opérations) et plus proche que les caches L1.

Vous vous demandez peut-être pourquoi ces SRAM sont-elles si petites? Pourquoi ne sont-ils pas en mégaoctets? Ensemble, les caches de données et d'instructions occupent presque la même zone sur la puce que les blocs logiques principaux, de sorte que leur augmentation conduira à une augmentation de la surface totale de la puce.

Mais la principale raison de leur taille de plusieurs kilo-octets est qu'au fur et à mesure que la capacité de la mémoire augmente, le temps nécessaire pour rechercher et récupérer des données augmente. Le cache L1 doit être très rapide, il y a donc un compromis entre la taille et la vitesse - au mieux, il faut environ 5 cycles d'horloge pour obtenir les données de ce cache (plus pour les valeurs en virgule flottante).

Cache L2 de Skylake: 256 Ko de SRAM

Mais si c'était le seul cache à l'intérieur du processeur, ses performances se heurteraient à un obstacle inattendu. C'est pourquoi une autre couche de mémoire est intégrée aux noyaux: le cache de niveau 2. Il s'agit d'un bloc de stockage généralisé contenant des instructions et des données.

Il est toujours plus grand que le niveau 1: dans les processeurs AMD Zen 2 , il faut jusqu'à 512 Ko pour fournir suffisamment de données pour les caches de niveau inférieur. Cependant, la grande taille nécessite des sacrifices - il faut environ deux fois plus de temps pour trouver et transférer les données de ce cache par rapport au niveau 1.

À l'époque du premier Intel Pentium, le cache de niveau 2 était une puce distincte, soit installée sur une petite carte séparée (comme la mémoire DIMM), soit intégrée à la carte mère principale. Peu à peu, il s'est déplacé dans le boîtier du processeur lui-même et, finalement, il a été entièrement intégré dans le cristal de la puce; cela s'est produit à l'ère des processeurs tels que le Pentium III et l'AMD K6-III.

Cette réalisation a été rapidement suivie par un autre niveau de cache nécessaire pour prendre en charge les niveaux inférieurs, et elle est arrivée juste à temps pour l'apogée des puces multicœurs.

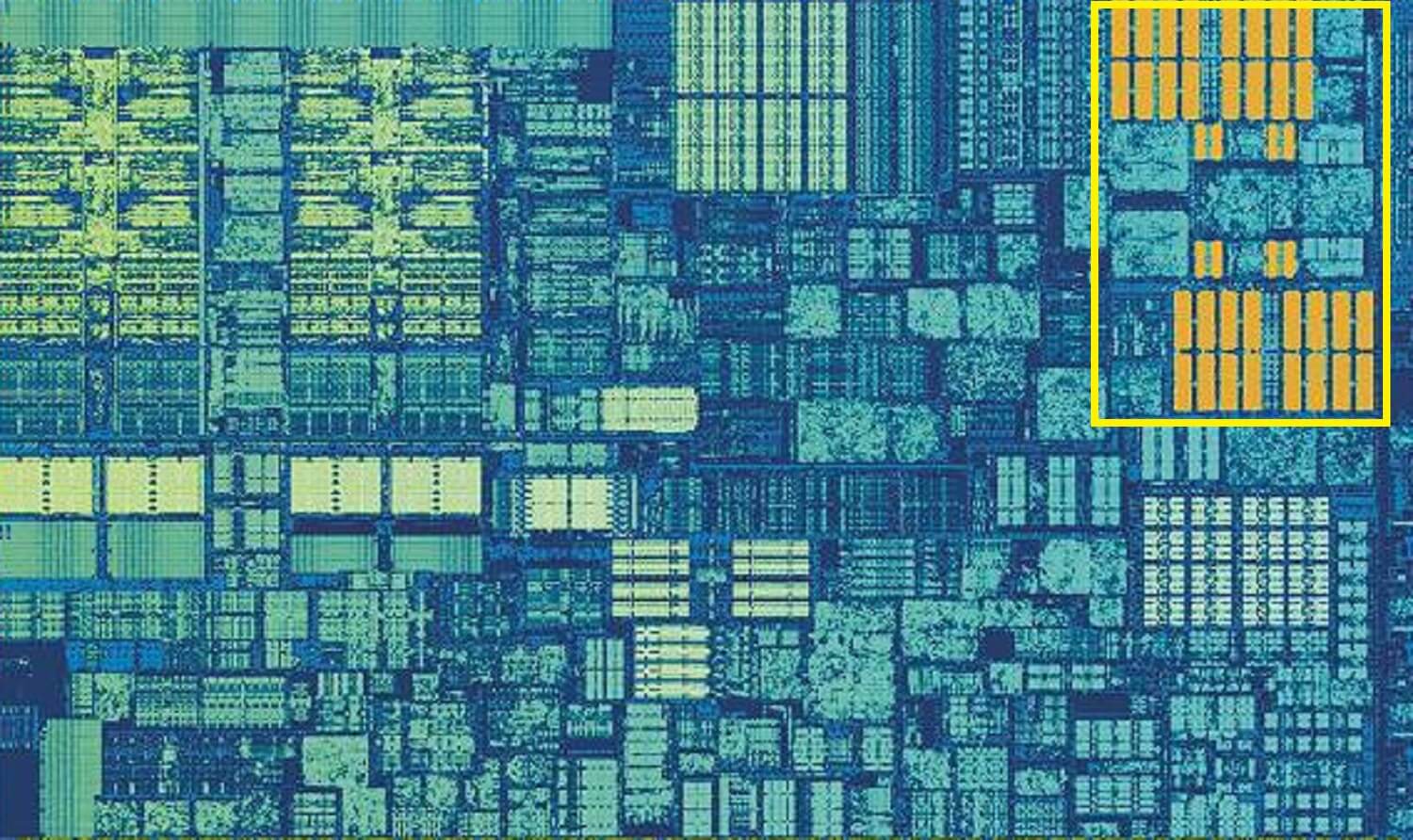

Puce Intel Kaby Lake. Source: Wikichip

Cette image de la puce Intel Kaby Lake montre quatre cœurs à gauche (le GPU intégré occupe près de la moitié de la matrice et se trouve à droite). Chaque noyau a son propre ensemble «personnel» de caches de niveau 1 et 2 (surlignés dans des cases blanches et jaunes), mais ils ont également un troisième ensemble de blocs SRAM.

Le cache de troisième niveau (niveau 3), bien que situé directement à côté d'un cœur, est complètement commun à tous les autres - chaque cœur peut accéder librement au contenu du cache L3 d'un autre cœur. Il est beaucoup plus volumineux (2 à 32 Mo), mais aussi beaucoup plus lent, avec une moyenne de plus de 30 cycles, en particulier lorsque le noyau a besoin d'utiliser des données résidant dans un bloc de cache éloigné.

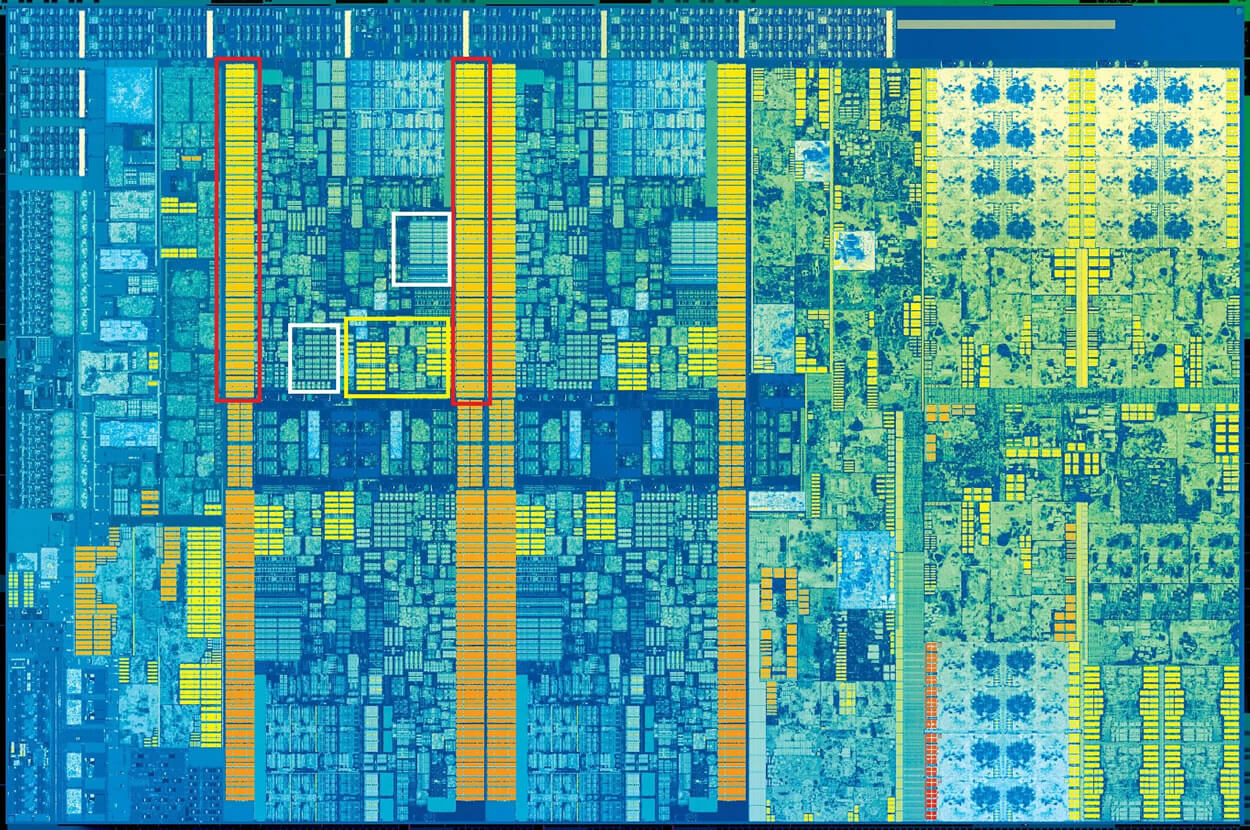

Vous trouverez ci-dessous un noyau de l'architecture AMD Zen 2: caches de données et d'instructions de niveau 1 de 32 Ko (dans les cases blanches), cache de niveau 2 de 512 Ko (dans les cases jaunes) et un énorme bloc de cache L3 de 4 Mo (dans la case rouge).

Zoom sur un seul cœur d'un processeur AMD Zen 2. Source: Fritzchens Fritz

Mais attendez: comment 32 Ko peuvent- ils occuper plus d'espace physique que 512 Ko? Si le niveau 1 stocke si peu de données, pourquoi est-il disproportionné par rapport aux caches L2 et L3?

Pas seulement des chiffres

Le cache améliore les performances en accélérant le transfert des données vers des blocs logiques et en conservant une copie des instructions et des données fréquemment utilisées à proximité. Les informations stockées dans le cache sont divisées en deux parties: les données elles-mêmes et l'endroit où elles se trouvent à l'origine dans la mémoire / stockage système - cette adresse est appelée balise de cache .

Lorsque le processeur effectue une opération qui a besoin de lire ou d'écrire des données de / vers la mémoire, il commence par vérifier les balises dans le cache de niveau 1. Si les données requises sont là (un succès de cache s'est produit ), alors ces données sont presque Immediatement. Un échec de cache se produit lorsque la balise requise n'est pas trouvée au niveau le plus bas du cache.

Une nouvelle balise est créée dans le cache L1, et le reste de l'architecture du processeur prend le relais, en regardant dans d'autres niveaux du cache (jusqu'au stockage principal, si nécessaire) pour les données de cette balise. Mais pour libérer de l'espace dans le cache L1 pour cette nouvelle balise, quelque chose doit être jeté dans L2.

Il en résulte un brassage quasi constant des données, effectué en seulement quelques cycles d'horloge. La seule façon d'y parvenir est de créer une structure complexe autour de la SRAM pour gérer la gestion des données. En d'autres termes, si le cœur du processeur se composait d'un seul ALU, le cache L1 serait beaucoup plus simple, mais comme il y en a des dizaines (et beaucoup d'entre eux jonglent avec deux flux d'instructions), le cache nécessite de nombreuses connexions pour déplacer les données.

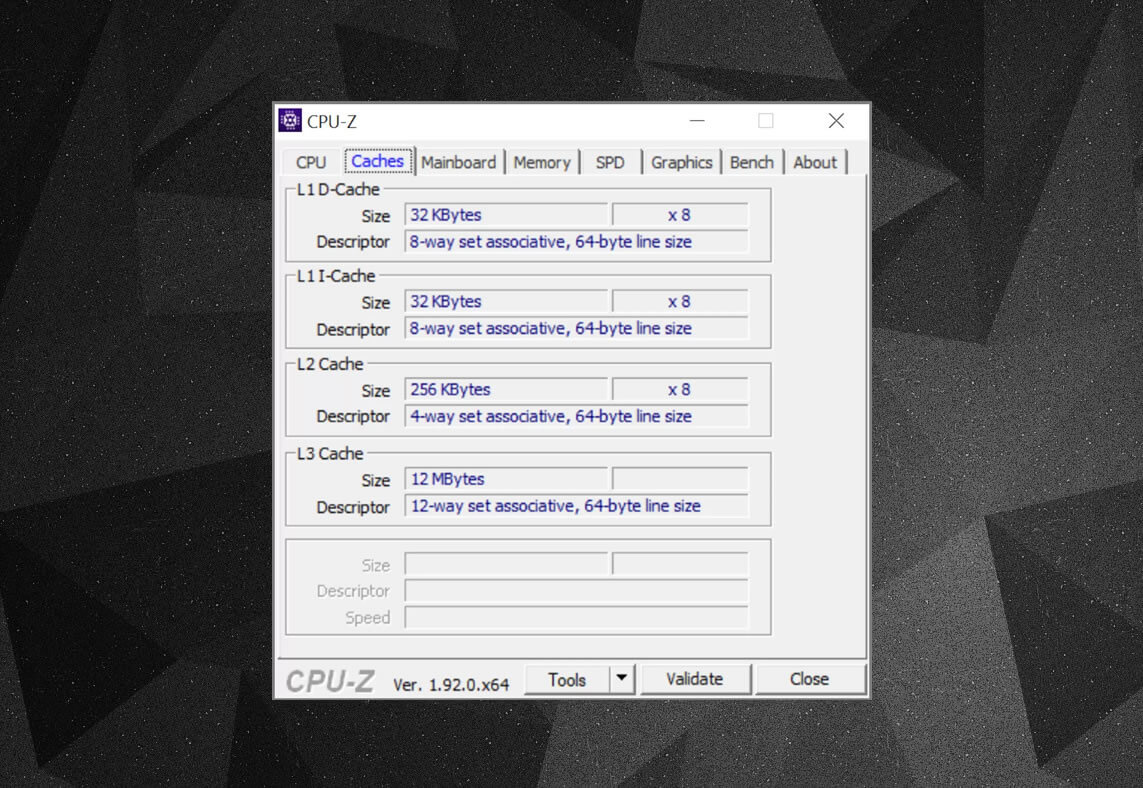

Vous pouvez utiliser des programmes gratuits tels que CPU-Z pour examiner les informations du cache dans le processeur de votre ordinateur . Mais que signifient toutes ces informations? Un élément important est l'étiquette associative définie , qui indique les règles utilisées pour copier des blocs de données de la mémoire système vers le cache.

Les informations de cache ci-dessus concernent Intel Core i7-9700K . Chacun de ses caches de niveau 1 est divisé en 64 petits blocs, appelés ensembles , et chacun de ces blocs est également divisé en lignes de cache.(64 octets de taille). «Ensemble associatif» signifie qu'un bloc de données du système est lié aux lignes de cache dans un ensemble particulier, et ne peut pas être librement lié à un autre endroit.

«8 voies» signifie qu'un bloc peut être associé à 8 lignes de cache dans l'ensemble. Plus le niveau d'associativité est élevé (c'est-à-dire, plus le «chemin» est grand), plus il y a de chances qu'un cache de cache lors d'une recherche de processeur, et moins la perte causée par les échecs de cache. Les inconvénients d'un tel système sont la complexité et la consommation d'énergie accrues, ainsi que des performances inférieures, car plus de lignes de cache doivent être traitées pour chaque bloc de données.

Cache inclus L1 + L2, cache victime L3, politiques de réécriture, il y a même ECC. Source: Fritzchens Fritz

Un autre aspect de la complexité du cache concerne la manière dont les données sont stockées entre les différents niveaux. Les règles sont définies dans la politique d'inclusion . Par exemple, les processeurs Intel Core ont des caches L1 + L3 entièrement inclusifs . Cela signifie que certaines données du niveau 1, par exemple, peuvent être présentes au niveau 3. Cela peut sembler être un gaspillage d'espace de cache précieux, mais l'avantage est que si le processeur manque l'étiquette du niveau inférieur, il n'a pas besoin recherchez le niveau supérieur pour les données.

Dans les mêmes processeurs, le cache L2 est non inclusif: toutes les données qui y sont stockées ne sont copiées sur aucune autre couche. Cela économise de l'espace, mais amène le système de mémoire de la puce à rechercher une balise manquante dans L3 (qui est toujours beaucoup plus grande). Les caches des victimes sont similaires en principe, mais ils sont utilisés pour stocker des informations provenant de niveaux inférieurs. Par exemple, les processeurs AMD Zen 2 utilisent le cache victime L3, qui stocke simplement les données de L2.

Il existe d'autres stratégies de cache, telles que l'écriture de données à la fois dans le cache et dans la mémoire système principale. Celles-ci sont appelées politiques d'écriture ; la plupart des processeurs modernes utilisent des caches de réécriture- cela signifie que lorsque des données sont écrites dans la couche de cache, il y a un délai avant d'en écrire une copie dans la mémoire système. Le plus souvent, cette pause dure aussi longtemps que les données restent dans le cache - la RAM ne reçoit ces informations que lorsqu'elle est "extraite" du cache.

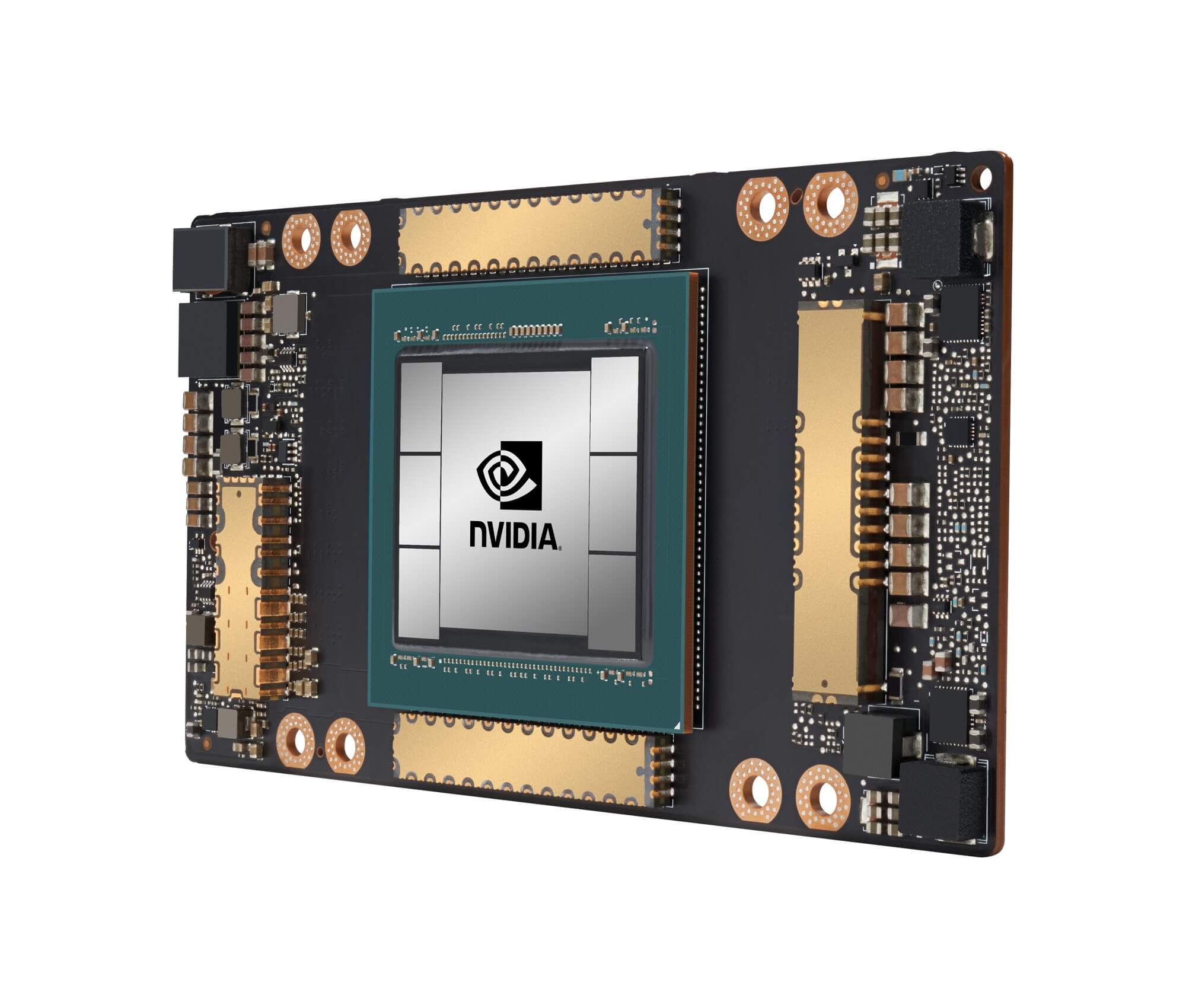

GPU Nvidia GA100 avec 20 Mo de cache L1 et 40 Mo de cache L2

Pour les concepteurs de processeurs, le choix de la taille, du type et de la politique du cache consiste à équilibrer le disque pour augmenter la puissance du processeur avec une complexité et une empreinte de puce croissantes. S'il était possible de créer des caches associatives de niveau 1 de 20 Mo de 1000 canaux de sorte qu'elles n'occupent pas la zone de Manhattan (et ne consomment pas la même quantité d'énergie), alors nous aurions tous des ordinateurs avec de telles puces!

Le niveau le plus bas de caches dans les processeurs modernes est resté pratiquement inchangé au cours de la dernière décennie. Cependant, la taille du cache de niveau 3 continue d'augmenter. Si vous aviez 999 $ pour un Intel i7-980X il y a dix ans, vous pourriez avoir un cache de 12 Mo. Aujourd'hui pour la moitié de ce montantdisponible à l' achat de 64 MB .

Pour résumer, le cache est un appareil absolument essentiel et génial. Nous n'avons pas couvert d'autres types de caches dans le CPU et le GPU (par exemple, les tampons de traduction associatifs ou les caches de texture), mais comme ils ont tous la même structure simple et la même disposition des niveaux, il ne sera pas difficile de les comprendre.

Avez-vous eu un ordinateur avec cache L2 sur la carte mère? Qu'en est-il des cartes filles Pentium II et Celeron (par exemple 300a ) à fente ? Vous vous souvenez de votre premier processeur L3 partagé?

La publicité

Notre société propose à la location des serveurs équipés de processeurs Intel et AMD. Dans ce dernier cas, ce sont des serveurs épiques! VDS avec AMD EPYC , fréquence centrale du processeur jusqu'à 3,4 GHz. La configuration maximale est de 128 cœurs de processeur, 512 Go de RAM, 4000 Go de NVMe.