J'ai déjà parlé des jeunes mariés Vladislav et Elena Sharshin, qui, avec leur collègue Andrey Papushin, Intel ont emmenés en Californie pour la victoire d'argent au concours InnovateFPGA. Leur interview est dans le laboratoire "Digital Synthesis" récemment publié . Nous allons utiliser ce labnik lors d'un séminaire destiné aux écoliers et aux étudiants juniors, qui aura lieu les 15 et 17 septembre à l'exposition ChipEXPO à Skolkovo . Si vous allez répéter (ou dépasser) la réalisation du Sharshin et Papushin, ou simplement devenir un concepteur FPGA ou ASIC sans quitter Santa Clara, alors participer à un séminaire, ou même simplement regarder les instructions initiales de cet article, vous aidera à démarrer.

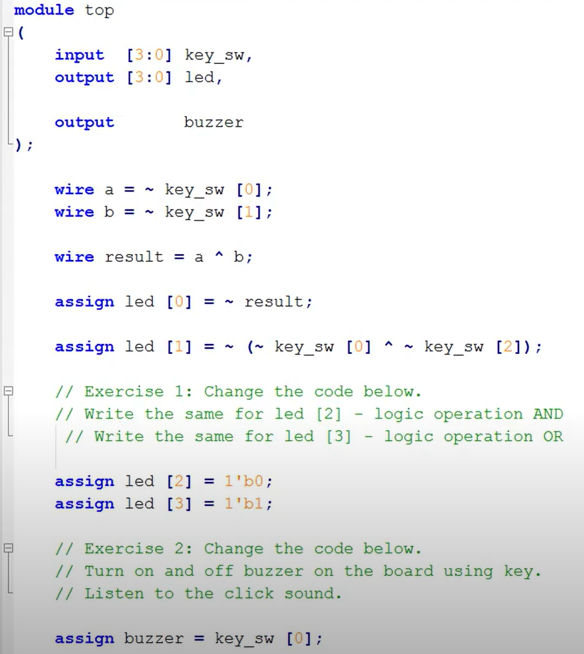

Beaucoup de ceux qui se sont inscrits au séminaire ont déjà reçu des cartes FPGA (elles sont distribuées par le département éducatif de RUSNANO) pour réussir le prérequis théorique . Il serait maintenant très souhaitable que les participants au séminaire installent à l'avance Intel FPGA Quartus (ou, si quelqu'un n'aime pas Intel / Altera, puis Xilinx Vivado) et exécutent au moins un test primitif dessus. Pas même une LED clignotante, mais généralement une porte XOR. Si tout le monde le fait à l'avance, alors lors du séminaire, nous discuterons de problèmes non triviaux tels que "Je n'ai pas de pilote pour USB Blaster", mais de quelque chose de plus intéressant, par exemple, ce qui est demandé pour une interview pour le poste de RTL Logic Designer chez NVidia, AMD, Apple et d'autres entreprises.

Donc, tout d'abord, le séminaire a une organisation sur github . Vous pouvez cloner le référentiel ce2020labs à partir de là et utiliser les fichiers du répertoire before pour tester votre carte, installer Quartus ou Vivado, les pilotes et résoudre les problèmes avec le programmeur. Le répertoire contient des fichiers pour sept cartes: cinq cartes avec Intel FPGA (deux variantes OMDAZZ / rzrd, deux variantes ZEOWAA et Terasic DE10-Lite), et deux cartes avec Xilinx (Basys3 et Nexys4).

Si vous ne souhaitez pas utiliser GitHub, vous pouvez simplement télécharger le zip à partir d'ici . Tous ces fichiers fonctionneront avec les versions Windows et Linux de Quartus et Vivado.

Pour installer Quartus, vous pouvez regarder une vidéo détaillée de Sergei Ivants, doyen de la Faculté des technologies électroniques et de l'information de l'Université technologique nationale de Tchernihiv:

Vidéo:

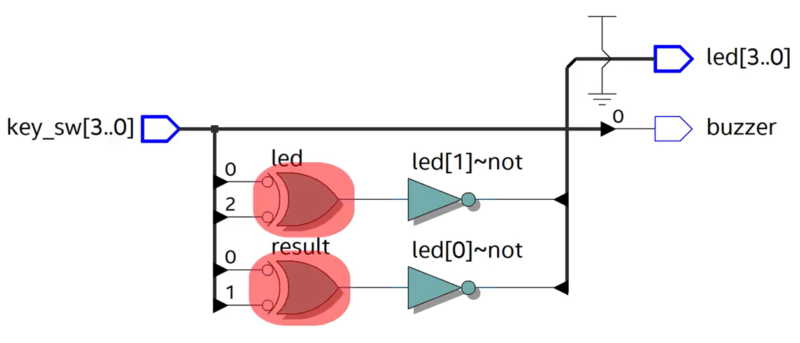

Et une vidéo sur la synthèse de l'exemple le plus simple de la description en langage Verilog:

Avec une description détaillée de ce qui est quoi:

Le seul problème est que cette vidéo ne couvre pas très bien l'utilisation du programmeur (et les problèmes avec ses pilotes). Par conséquent, vous trouverez peut-être utile de regarder une autre vidéo, également de Sergey, où il décrit l'utilisation d'USB Blaster après l'éditeur de schémas. Il faut dire ici que l'entrée schématique est tombée en désuétude par les concepteurs de la microélectronique numérique au début des années 1990 (tout le monde est passé au design en utilisant les langages de description matérielle Verilog et VHDL), mais Sergei a néanmoins décidé de le montrer purement pour qu'un étudiant qui commence à se lancer dans la conception numérique le fasse immédiatement intuitivement. Je me suis rendu compte que nous concevions des circuits et non que nous écrivions des programmes, bien que le code de verlog soit similaire au code d'un langage de programmation.

Voici une vidéo de l'entrée schématique, à la fin de laquelle l'utilisation du programmeur est décrite:

Avant, pendant et après le séminaire à ChipEXPO à Skolkovo, nous continuerons à télécharger divers documents, mais pour tout regarder (y compris, par exemple, une mini-conférence sur l'organisation des équipes de développement de puces dans la Silicon Valley), il vaut mieux s'inscrire.