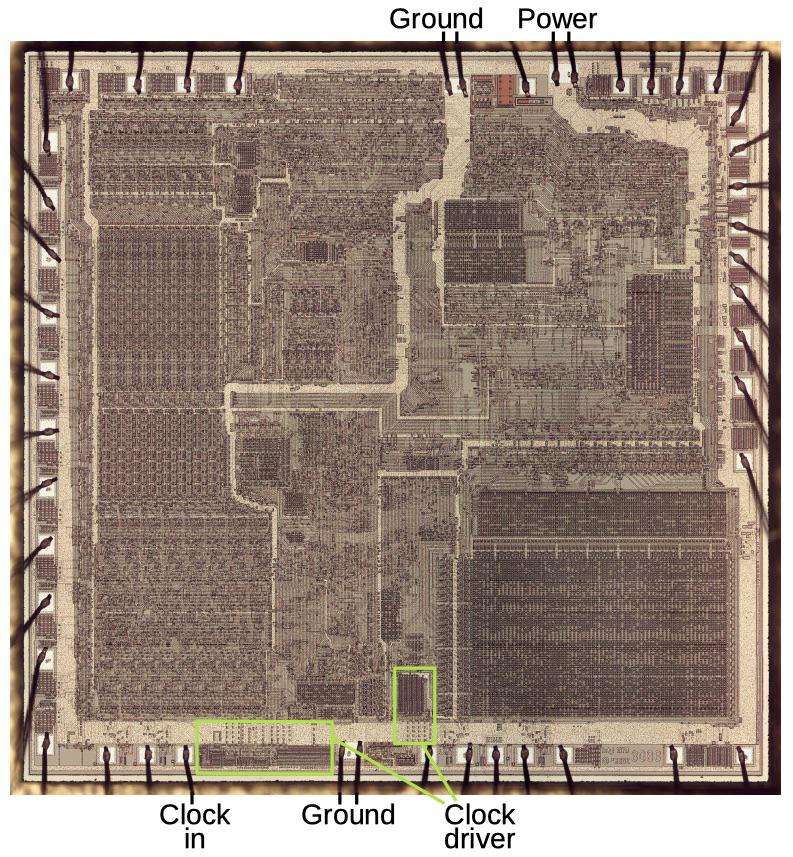

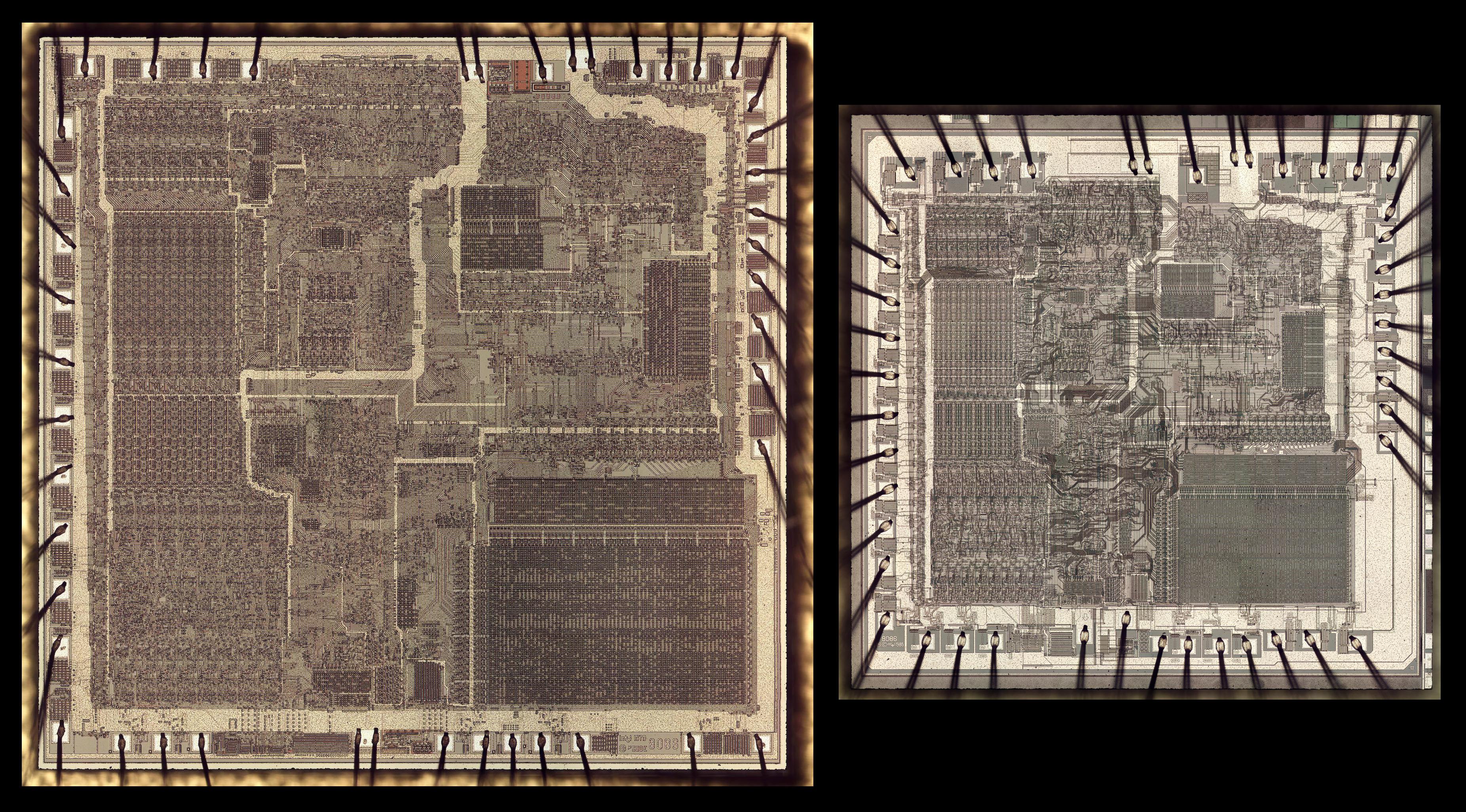

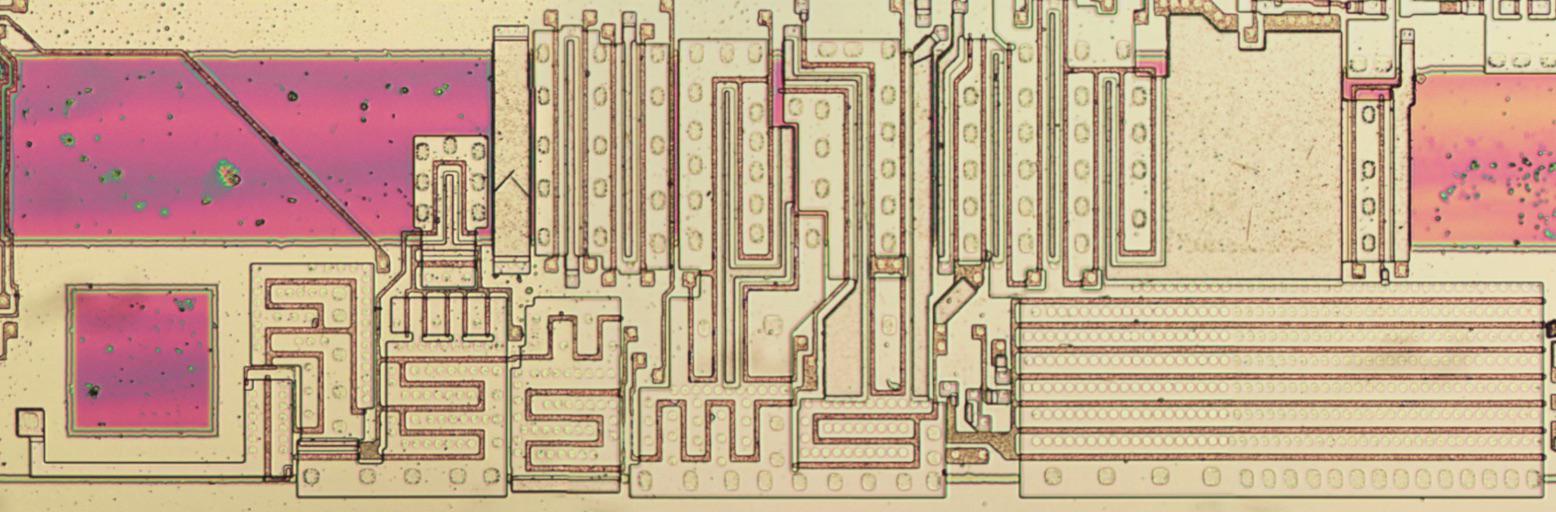

La photo ci-dessous montre un cristal 8086 au microscope. Une couche métallique est visible sur le dessus de la puce, sous laquelle un substrat de silicium et une couche de polysilicium avec des conducteurs sont cachés. Le long de l'extérieur du périmètre du cristal, un petit fil de liaison relie les tampons de cristal aux pattes extérieures. Le 8086 a un bloc d'alimentation en haut et des tampons de terre en haut et en bas. Chacun d'eux a deux fils pour souder les fils, ce qui double le courant supporté. De larges chemins métalliques sont visibles s'étendant depuis les bornes d'alimentation et de masse. Ils distribuent l'énergie à travers la puce.

Photo du cristal 8086, où vous pouvez voir le point d'alimentation (en haut) et les contacts de masse (en haut et en bas). Les circuits d'horloge sont situés en bas.

Il y a deux signaux d'horloge internes responsables de la synchronisation dans le 8086. Un oscillateur externe envoie des signaux d'horloge au 8086 via le pad d'horloge d'entrée ci-dessous. Le générateur d'horloge interne fournit deux signaux d'horloge à courant élevé basés sur des signaux externes. Notez que le pilote d'horloge occupe une grande empreinte sur la puce.

Dans cet article, je décrirai comment le 8086 redirige l'énergie et les signaux d'horloge dans toute la puce, et comment le circuit d'horloge génère les impulsions d'horloge nécessaires.

Distribution d'énergie

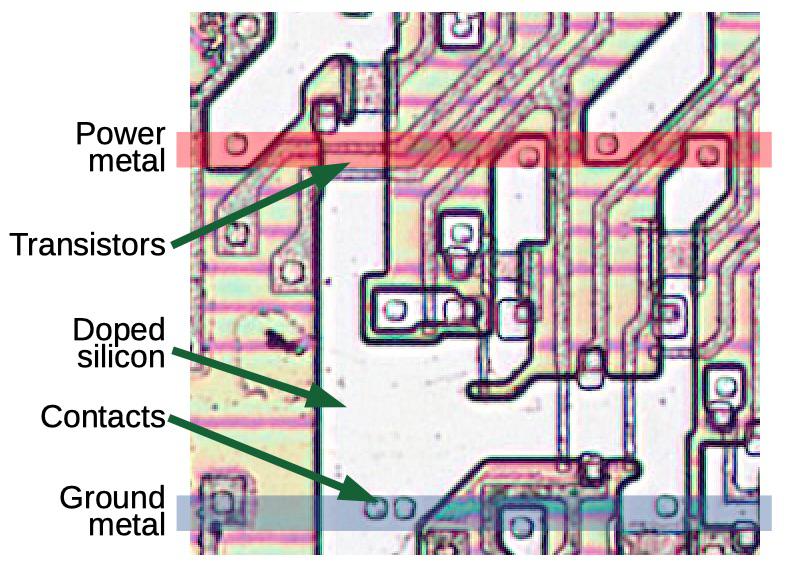

8086 se compose de trois couches, dont chacune peut accueillir des conducteurs. La couche de métal sur le dessus est la meilleure pour cela en raison de la faible résistance du métal. Sous le métal se trouve une couche de conducteurs en polysilicium, constituée d'un type spécial de silicium. La résistance du polysilicium est supérieure à celle du métal, mais il peut toujours être utilisé pour transmettre des signaux à travers la puce. Des transistors sont formés sur le substrat de silicium. La résistance du silicium est relativement élevée, il n'est donc utilisé que pour transmettre des signaux sur de courtes distances - par exemple, à l'intérieur d'une porte.

La répartition de la puissance dans une puce comme la 8086 est un casse-tête topologique. En raison de sa faible résistance, la couche métallique reste la seule couche pratiquement utile pour le câblage d'alimentation et de terre. Presque toutes les portes de la puce doivent être alimentées et mises à la terre. Et comme la puce a une couche métallique, la puissance et la terre ne peuvent pas se croiser.

Presque toutes les portes de la puce ont besoin d'alimentation et de mise à la terre car la porte MOS standard nécessite de la terre pour son réseau pull-down et de l'alimentation pour sa résistance pull-up. Cependant, il existe quelques exceptions. 8086 utilise des portes logiques dynamiques, en particulier dans ALU - pour la vitesse. Ces portes sont attirées vers le haut par le signal de synchronisation, elles n'ont donc pas besoin d'une alimentation directe. Le 8086 utilise également plusieurs portes XOR au niveau des transistors de traversée, qui sont abaissées par le signal entrant, de sorte qu'elles n'ont pas besoin de masse.

La ROM à microcode forme une grande partie de la puce qui n'a pas besoin d'alimentation, seulement de la terre. Cela est dû au fait que chaque rangée de ROM est implémentée comme une très grande porte NON-OU et que la puissance qui la tire vers le haut est située sur le bord droit. Par conséquent, toutes les portes de la ROM sont alimentées et mises à la terre, bien qu'il semble que la ROM ne dispose pas d'une connexion d'alimentation.

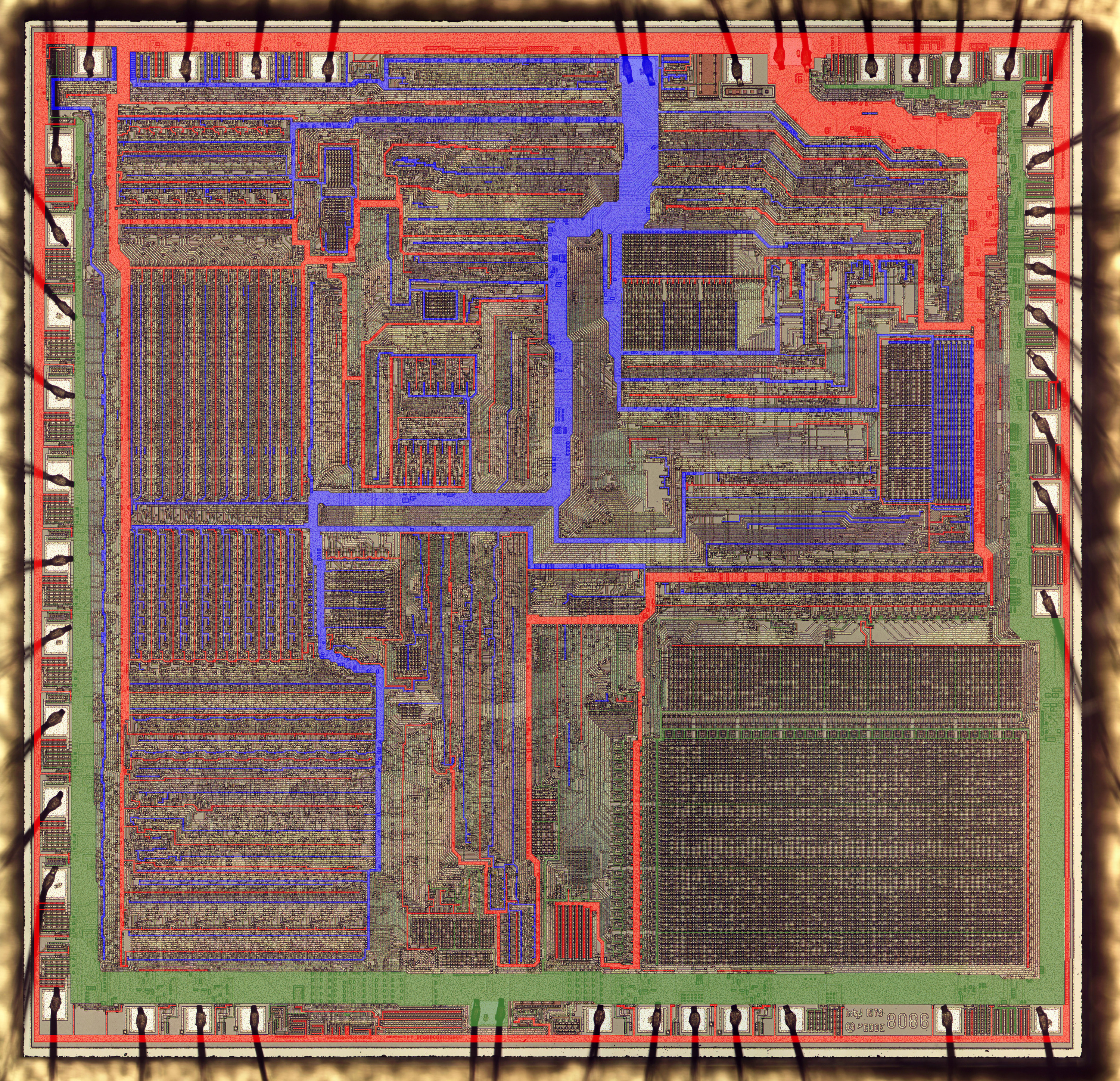

Le schéma ci-dessous montre les conducteurs métalliques du 8086. Le bloc d'alimentation connecté à la broche d'alimentation en haut est indiqué en rouge. Une puissante branche de nourriture descend et vers la droite, puis elle se divise en plusieurs branches. L'alimentation passe également le long du bord de l'ensemble de la puce, alimentant les broches d'E / S.

Avec les circuits intégrés, il arrive souvent que l'alimentation et la masse soient situées dans des coins opposés ou sur des côtés opposés de la puce. Cet agencement facilite le routage des voies électriques et au sol qui ne se croisent pas. Le 8086 a un positionnement légèrement inhabituel de l'alimentation et de la masse sur des broches diagonalement opposées, et la deuxième masse plus proche de la broche d'alimentation. Les réseaux électriques et les terres sur la puce se ramifient comme des arbres. Ces réseaux se ramifient et, comme des doigts entrelacés, atteignent toutes les parties de la puce.

Alimentation (rouge) et masse (bleu, vert) sur la couche métallique de la puce

Il y a deux contacts de masse. Les pistes marquées en bleu se connectent à la broche de masse supérieure et les vertes en bas. Les chemins de terre balisés en bleu montrent une épaisse ramification passant par le centre de la puce et se ramifiant de manière complexe dans toutes les directions. Les voies vertes longent les côtés inférieur, gauche et droit de la puce, supportant les broches d'E / S et se connectant à la ROM du microcode en bas à droite.

En s'éloignant de la source d'alimentation et en se rapprochant des points d'extrémité, les conducteurs d'alimentation deviennent plus minces et le courant diminue. Cela peut être vu du conducteur d'alimentation aux broches d'adresse et de données ci-dessous. A gauche sous les contacts, le conducteur avec le sol est très large, mais il se rétrécit progressivement en allant vers la droite. En d'autres termes, à gauche, le conducteur doit conduire le courant à partir de tous les contacts, et à l'extrême droite, à partir d'un seul.

La connexion des broches d'adresse et de données à la terre s'amincit (côté gauche de la puce tourné à 90 °) La

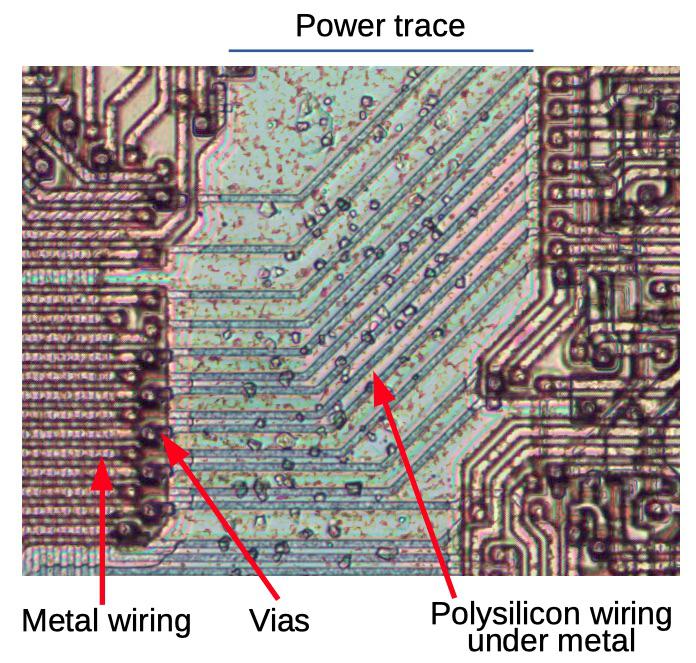

couche métallique est utilisée pour transporter de nombreux signaux, pas seulement l'alimentation et la terre. En raison de sa faible impédance, c'est la meilleure couche de transmission de signal. Cependant, l'utilisation répandue de conducteurs d'alimentation et de terre limite les capacités de la couche métallique. Pour éviter le croisement, la plupart des chemins de signal sur la couche métallique sont parallèles aux chemins d'alimentation. Une couche de silicium polycristallin en dessous est utilisée pour la transmission de signaux perpendiculaires. Mais que se passe-t-il si un conducteur métallique doit traverser une piste d'alimentation ou de masse? La solution est de le dessiner par le bas [crossunder]. Le signal descend au niveau du silicium polycristallin, traverse la piste, puis remonte, comme illustré ci-dessous.

Ces traversées de fond sont utilisées dans de nombreux cas, non seulement avec de la nourriture. Cependant, le plus souvent, il s'agit de nutrition. En règle générale, des conducteurs métalliques sont utilisés pour transmettre des signaux dans une direction, et des conducteurs en polysilicium sont utilisés pour transmettre des signaux dans la direction perpendiculaire. À différents endroits de la puce, ces directions changent et dépendent de la direction dominante de transmission du signal. Par conséquent, pour la plupart, les signaux voyagent sans entrave. Et pourtant, ils doivent souvent passer d'une couche à l'autre.

Les signaux sur la couche métallique traversent les chemins d'alimentation par le bas via une couche de polysilicium

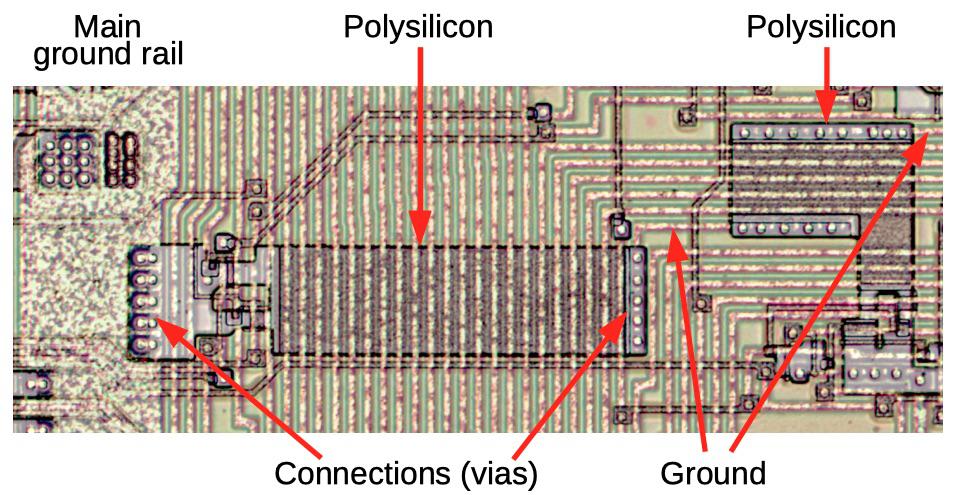

Si l'alimentation et la terre sont presque entièrement acheminées vers la couche métallique, à certains endroits, ce circuit est interrompu et les traces situées en dessous sont utilisées pour fournir de l'énergie. Cela se produit plus souvent dans les toutes dernières sections des pistes, où le courant est déjà faible. Un exemple est montré ci-dessous - où le sol passe deux fois sous la couche métallique en utilisant des conducteurs en polysilicium. Pour réduire la résistance, ces chemins de dérivation sont beaucoup plus larges que les chemins de signal et utilisent également du silicium et du polysilicium ensemble. Les petits cercles sont des contacts [via] entre les couches de métal et de polysilicium.

Photo composite montrant des chemins de contournement au sol traversant du polysilicium sous les chemins de signal.

La couche de silicium joue un rôle mineur dans le câblage d'alimentation. En particulier, de nombreuses portes sont étirées pour atteindre l'alimentation et la masse de l'autre côté. La photo ci-dessous montre les portes 8086. Notez les grandes zones de silicium dopé (blanc) qui sont tirées pour atteindre le sol et les rails d'alimentation. Seule une petite fraction du silicium est utilisée pour les transistors, et tout le reste semble être un gaspillage d'espace. Cependant, ces sections vides de silicium relient les grilles à des conducteurs métalliques qui fournissent l'alimentation et la terre. Le silicium ayant une résistance relativement élevée, de larges zones sont utilisées à cet effet et les joints eux-mêmes s'étendent sur de courtes distances.

Les grilles en silicium dopé peuvent être allongées pour atteindre les rails d'alimentation et de masse. Pour cette photo, la couche métallique a été supprimée.

Une fois que le 8086 a été mis à jour et physiquement rétréci, il a eu d'autres problèmes de câblage d'alimentation. Avec l'amélioration de la technologie de fabrication, Intel a mis à l'échelle les cristaux - laissant les circuits inchangés, mais les a réduits proportionnellement. Malheureusement, la réduction de la taille des pistes d'alimentation réduit également le courant maximal. Pour résoudre ce problème, les chemins d'alimentation autour de la puce ont été renforcés et les circuits internes et le câblage ont été réduits. Cela peut être vu sur la photo ci-dessous - par exemple, il y a beaucoup plus de pistes d'alimentation dans le coin inférieur droit du plus petit 8086.

Deux versions de 8086 à la même échelle. Le cristal de droite est une version plus récente, de taille réduite.

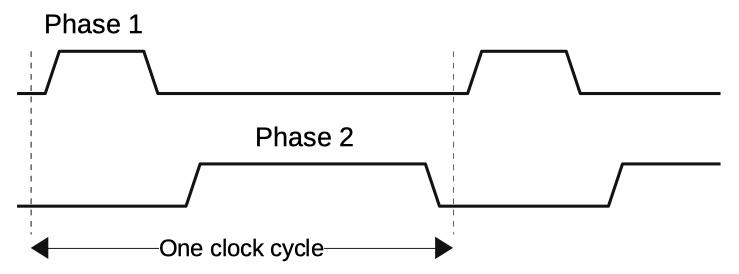

Presque tous les ordinateurs utilisent des signaux d'horloge pour contrôler la synchronisation du processeur. Le 8086, comme de nombreux microprocesseurs, utilise un pilote d'horloge biphasé en interne. Un pilote d'horloge biphasique a deux horloges - lorsque la première est haute, la seconde est basse, et vice versa, comme illustré ci-dessous. Certains circuits sont activés avec le premier signal de synchronisation et d'autres avec le second. Le schéma de fonctionnement du 8086 implique qu'il n'y a pas de chevauchement entre les deux phases des signaux de synchronisation et leur asymétrie - il y a un écart entre les moments où un signal de synchronisation devient bas et le second monte.

Un pilote d'horloge biphasé se compose de deux signaux d'horloge de polarité opposée

Bien que presque tous les ordinateurs utilisent des signaux d'horloge pour la synchronisation, la machineL'architecture IAS (populaire dans les années 1950) était asynchrone et fonctionnait sans signaux d'horloge. Au lieu de cela, chaque circuit, une fois terminé, a envoyé une impulsion au suivant, déclenchant l'étape suivante. Beaucoup d'ordinateurs du début des années 1950 étaient basés sur cette architecture, y compris CYCLONE, ILLIAC, JOHNNIAC, MANIAC, SEAC et IBM 701. Les recherches sur les possibilités de l'informatique asynchrone se poursuivent , mais les systèmes synchrones dominent certainement.

Les processeurs, entre autres, utilisent des signaux d'horloge pour éviter un retour indésirable dans les circuits. Par exemple, considérons un compteur logiciel dont la chaîne incrémente sa valeur et la renvoie au compteur. Vous ne voulez pas que la nouvelle valeur continue d'augmenter.

Une méthode consiste à utiliser des déclencheurs qui mettent à jour la valeur lorsque le signal passe de faible à élevé. Ensuite, le compteur sera mis à jour la seule fois, ce qui est nécessaire. Cependant, avec un signal de synchronisation biphasé, le circuit peut être réalisé sur des verrous sensibles au niveau, dont la conception est beaucoup plus simple que pour les déclencheurs sensibles aux changements de signal. Lorsque le premier signal de synchronisation est haut, la première moitié de la ligne reçoit une valeur d'entrée et effectue des calculs logiques. Lorsque le deuxième signal de synchronisation est élevé, la deuxième partie de la chaîne reçoit le résultat de la première moitié et effectue tous les calculs nécessaires, et la première partie est bloquée. Le fait est que seule la moitié de la chaîne peut être mise à jour à la fois, ce qui évite les retours indésirables.

Le 8086 a des exigences d'horloge d'entrée strictes, qui doivent être élevées pendant un tiers du temps. Typiquement, le 8086 a été généré par la puce 8284 et un cristal de quartz. La puce a divisé le signal d'horloge entrant par 3 pour fournir le cycle de service d'horloge de 33% requis par le 8086.

Dans les processeurs modernes, la disposition du signal d'horloge est très complexe car le signal doit voyager simultanément vers toutes les parties de la puce. Les processeurs modernes utilisent une hiérarchie de chemins d'horloge, équilibrent les temps de trajet le long de chaque chemin et fournissent souvent une mémoire tampon distincte pour chaque chemin. À titre de comparaison, la disposition du signal d'horloge du 8086 est simple, car sa fréquence d'horloge de 5 à 10 MHz est de plusieurs ordres de grandeur inférieure à celle des processeurs modernes. À ces fréquences relativement basses, la longueur du chemin n'a pas vraiment d'importance, de sorte que les impulsions d'horloge du 8086 peuvent suivre des chemins sinueux.

Étant donné que le 8086 utilisait la logique dynamique, il avait également une vitesse d'horloge minimale de 2 MHz. Si la fréquence est inférieure, il existe un risque de fuite de charge avant son renouvellement, ce qui peut entraîner des pannes. La fréquence d'horloge minimale n'était pas pratique du point de vue du débogage, car il était impossible de ralentir ou d'arrêter le signal d'horloge.

Synchroniser les chemins dans 8086. Le vert est la première synchronisation et le rouge est la seconde, avec la phase opposée

Le diagramme ci-dessus montre les chemins d'horloge du 8086. La phase 1 est verte et la phase 2 est rouge. Au bas de la puce, les circuits du pilote d'horloge apparaissent comme de grands points. À partir de là, les signaux de synchronisation se répartissent sur toute la puce. Pour la plupart, les deux phases d'horloge fonctionnent en parallèle, par opposition à l'alimentation et à la terre avec leurs branches opposées.

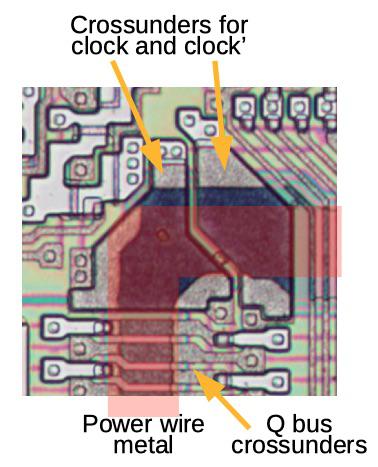

Étant donné que les signaux de synchronisation se déplacent vers toutes les parties de la puce, ils nécessitent beaucoup plus de courant que les signaux conventionnels et sont donc principalement acheminés vers la couche métallique. Lorsque les signaux de synchronisation doivent traverser les voies d'alimentation, ils passent en dessous, comme illustré ci-dessous. Notez que les solutions de contournement de synchronisation sont de forme irrégulière - elles sont beaucoup plus grandes que les solutions de contournement pour d'autres signaux, tels que le bus Q.

Les chemins de dérivation de l'alimentation sont assez grands. Le bus Q (transmission des commandes de la file d'attente de commandes au décodeur) en a beaucoup moins.

Pour fournir des signaux de synchronisation à courant élevé, leur circuit de mise en forme est construit sur de grands transistors. La photo ci-dessous compare l'un de ces transistors avec un transistor logique typique. Les transistors pilotes sont environ 300 fois plus grands, il est donc capable de fournir environ 300 fois le courant. Le transistor est composé de 10 transistors placés en parallèle - 10 lignes verticales en silicium polycristallin forment 10 grilles. Chaque signal de synchronisation est généré par une paire de grands transistors, dont l'un le tire vers le haut et l'autre le tire vers le bas.

Grand transistor dans le pilote d'horloge par rapport au transistor logique adjacent

La photo ci-dessous montre le schéma du générateur d'impulsions de synchronisation. Le circuit divise le signal d'horloge externe en deux phases, s'assure qu'elles ne se chevauchent pas et les amplifie. Le carré rose sur la gauche est une plate-forme pour un pilote d'horloge externe. Le signal traverse une série de transistors se terminant par les grands transistors de commande sur le côté droit. Les conducteurs bruns sont en polysilicium formant les grilles. De nombreux transistors ont des portes en zigzag, de sorte qu'un grand transistor tient dans un petit espace.

Circuit de pilote d'horloge sur puce. La couche métallique a été retirée. De grands transistors sont visibles. Broche d'entrée de synchronisation externe - carré rose à gauche.

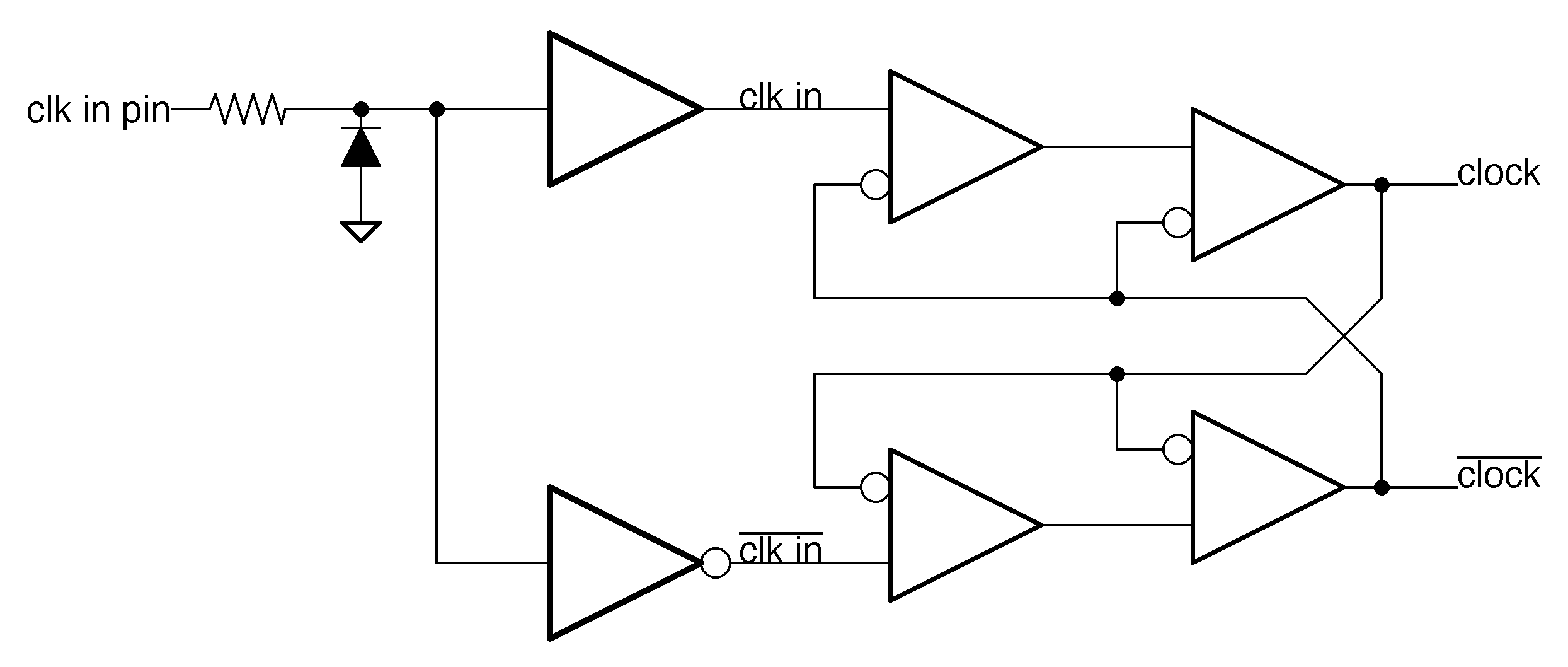

Vous trouverez ci-dessous un diagramme schématique légèrement simplifié du générateur d'horloge. Les triangles sont des pilotes à courant élevé constitués de deux ou trois transistors. L'entrée inverseuse (cercle) tire la sortie vers le bas. Sur le côté gauche de la broche de synchronisation d'entrée, il y a une petite résistance et une diode pour la protéger (tout comme les autres broches d'entrée). Le signal de synchronisation est ensuite divisé en phase inversée (en haut) et en phase inversée (en bas).

Schéma simplifié du générateur d'horloge 8086

Des circuits supplémentaires empêchent les signaux de synchronisation de se chevaucher: lorsqu'un signal est haut, cela, via une entrée inversée, fait que le deuxième signal est bas. Pour comprendre comment cela fonctionne, commençons par le moment où le signal sur la broche clk in est élevé. Les signaux clk in et clock sont hauts, tandis que ^ clk in ^ et ^ clock ^ sont bas. Maintenant, disons que le signal entrant à clk in devient faible, ce qui fait que le signal clk in diminue et que ^ clk in ^ augmente. Cependant, la sortie de ^ clock ^ ne peut pas augmenter tant que l'horloge n'est pas descendue. Après cela, le signal ^ clk in ^ passera par les drivers inférieurs, tirant ^ clock ^ vers le haut après deux délais de gate. Le fait est que l'horloge et ^ clock ^ ne commutent pas en même temps. Une fois que l'un est au niveau bas, il y a un délai avant que l'autre passe au niveau haut.En conséquence, nous obtenons des signaux de synchronisation sans chevauchement.

C'est une description assez approximative - en particulier, je ne suis pas sûr de ce qui se passe lorsqu'un transistor tire un signal vers le haut et un autre tire le même signal vers le bas. La simulation exacte du processus dépendra des tailles relatives des deux transistors.

Conclusion

Le 8086 utilise une configuration d'alimentation intéressante, mais les processeurs modernes fonctionnent à un niveau complètement différent. Si le 8086 avait besoin de 350 mA, alors un processeur moderne pourrait avoir besoin de plus de 100 A. Le 8086 a utilisé 3 de ses 40 pieds pour l'alimentation et la masse. Les processeurs Intel Core i5 modernes ont 128 broches d'alimentation et 377 - terre (sur un total de 1151 broches). Alors que les nombreuses couches métalliques des puces modernes résolvent les problèmes de câblage du 8086, elles introduisent de nouvelles complications telles que la division de la puce en sections d'alimentation, ce qui vous permet d'éteindre les sections inutilisées.

Dans les processeurs modernes avec leurs vitesses de plusieurs gigahertz, la disposition du signal de synchronisation est beaucoup plus compliquée, car un millimètre supplémentaire de piste peut affecter négativement le signal de synchronisation. Pour résoudre ces problèmes, les processeurs modernes utilisent des éléments tels que des arbres en H ou des réseaux de distribution d'horloge, plutôt que de simples pistes de branchement comme le 8086. Alors que le 8086 avait un simple circuit de génération d'horloge à deux phases, les processeurs modernes utilisent souvent une boucle à verrouillage de phase pour synthétiser l'horloge. , et de nombreux circuits dispersés dans la puce qui fournissent et contrôlent des signaux d'horloge. Mais si le 8086 est beaucoup plus simple que les processeurs modernes, il contient de nombreux exemples de circuits intéressants.