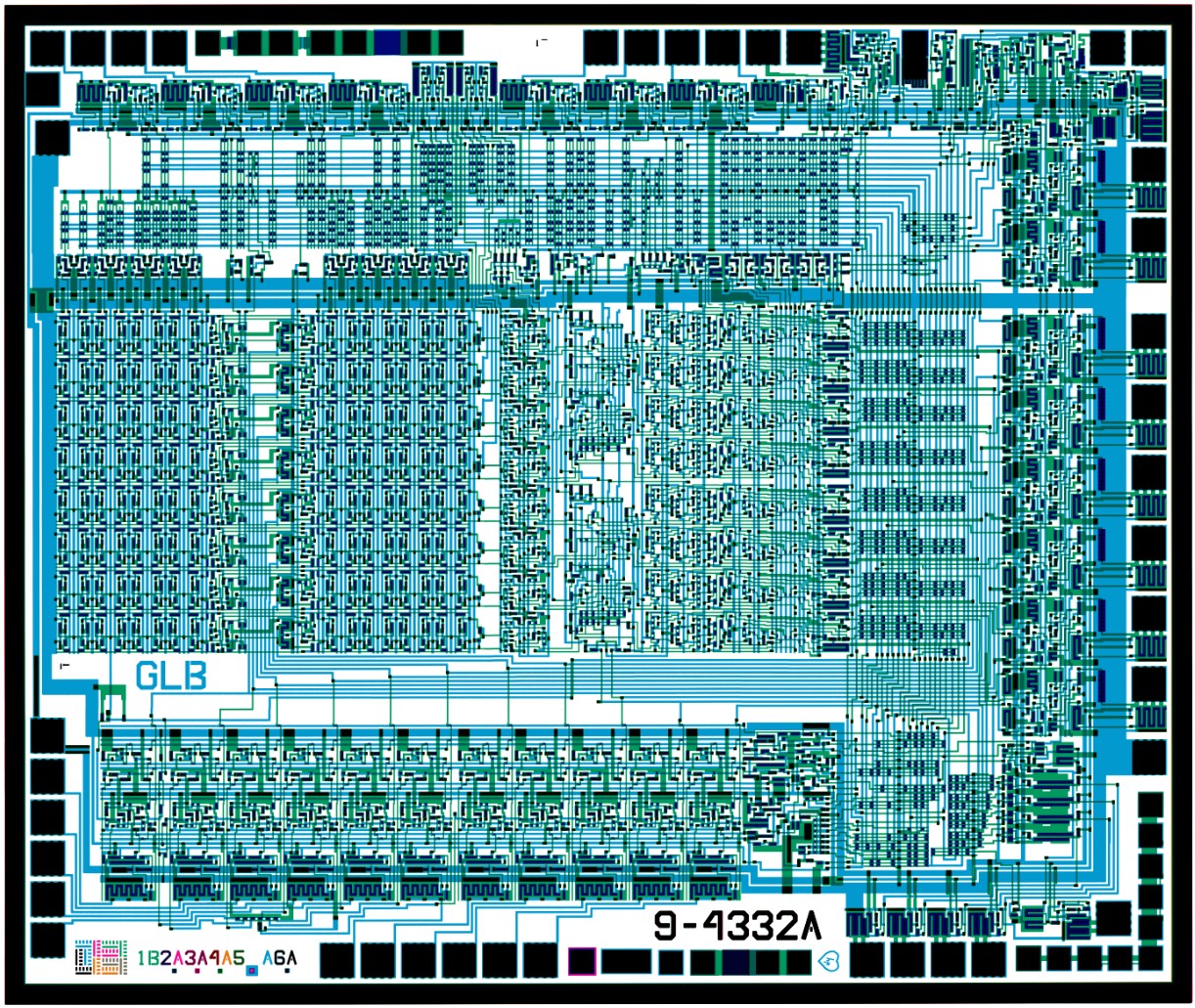

Photomasques combinés à nanoprocesseur. GLB à gauche du bus de données est les initiales des développeurs George Latham et Larry Bauer.

Le nanoprocesseur HP est un processeur presque oublié développé par Hewlett-Packard en 1974 (pour plus de détails, voir The Forgotten Ones: HP Nanoprocessor , HP9825.com et The HP 9845 Project ) en tant que microcontrôleur pour divers produits de l'entreprise. Il est étrange que ce processeur ne puisse même pas ajouter ou soustraire - c'est peut-être pourquoi ils ont décidé de l'appeler non pas un processeur, mais un «nanoprocesseur». Malgré ces limitations, Nanoprocessor contrôlait une variété d'appareils de Hewlett-Packard, des panneaux frontaux et des voltmètres aux analyseurs de spectre et aux terminaux d'acquisition de données.

J'ai déterminé que Nanoprocessor a été spécialement utilisé dans les produits suivants de Hewlett-Packard: HP 9845B Analyseurs de spectre, HP 3585A , HP 3325A Synthétiseur / Fonction Générateur , HP 9885 Lecteur de , HP 3070B Les données d' acquisition du terminal , HP 98034 HPIB interface pour calculatrice HP 9825, horloge temps réel HP 98035 pour ordinateur HP 9825, interface de lecteur de film HP 7970E , routeur HP 4262A , analyseur de spectre HP 3852 , voltmètre HP 3455A... Paul-Henning Camp m'a également dit que le nanoprocesseur était utilisé dans le synthétiseur / générateur de fonctions HP 3336 et le contrôleur de commutation HP 9411. La

principale caractéristique du nanoprocesseur était son faible coût et sa vitesse élevée: par rapport à son Motorola 6800 actuel, le nanoprocesseur coûtait 15 $, et non 360 $ , et a fait face aux tâches de gestion un ordre de grandeur plus rapide.

Fait intéressant, le concurrent de Nanoprocessor dans son développement était le Motorola 6800, et non le processeur d'Intel. La principale chose dont le nanoprocesseur pouvait se vanter était la vitesse: il fonctionnait à 4 MHz, étant donné que le 6800 fonctionnait à 1 MHz. Les deux processeurs ont pris 2 cycles d'horloge pour exécuter une instruction de base, tandis que le 6800 a pris jusqu'à 7 cycles d'horloge pour exécuter des instructions plus complexes.

Les développeurs du nanoprocesseur ont établi une comparaison de vitesse et ont suggéré que le nanoprocesseur pouvait lire six fois plus vite que le 6800 et gérer les interruptions plus de 16 fois plus rapidement. Cependant, à ce moment-là, il était supposé que le nanoprocesseur fonctionnerait à 5 MHz, et la puce réelle était légèrement inférieure à cette barre avec ses 4 MHz. Le prix préliminaire du nanoprocesseur s'appelait 15 $ contre 360 $ pour le Motorola 6800.

Je ne suis pas tout à fait d'accord pour dire que le nanoprocesseur peut être appelé un microcontrôleur, car il utilise une ROM externe avec un programme, alors qu'un microcontrôleur a généralement tout, y compris la ROM, sur une seule puce (dans cet aspect il ressemble à Intel 4004). Cependant, à presque tous les égards, le nanoprocesseur ressemble à un microcontrôleur: il est conçu pour une utilisation embarquée, son architecture Harvardet un ensemble d'instructions optimisé pour les E / S, il exécute des programmes à partir de la ROM avec un stockage de données minimal.

En ce qui concerne les ordinateurs qui ne pouvaient pas ajouter - l'ordinateur IBM 1620 de la taille d'une table de 1959 n'avait pas d'opération d'addition, mais utilisait un tableau de résultats pour cela. Son nom de code était CADET, et les gens l'ont déchiffré en plaisantant comme suit: «Je ne peux pas ajouter, je n'essaye même pas» [ne peut pas ajouter et n'essaye même pas].

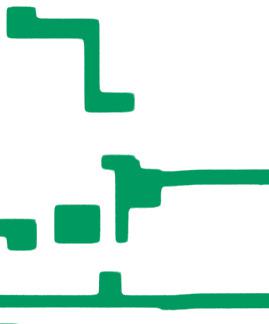

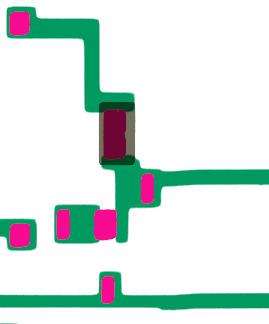

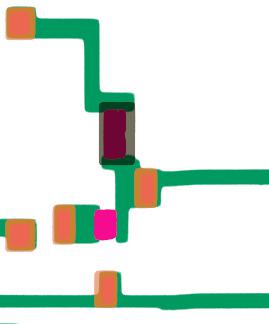

Récemment, le concepteur de puces Larry Bauer a publié six photomasques utilisés pour produire le nanoprocesseur, ainsi que des détails sur leur conception. Les photomasques ont été nettoyés et scannés dans The CPU Shack, puis nettoyés par Antoine Berkovichi (fichier PSD de 122 Mo peut être téléchargé à partir du lien). L'image composite des photomasques ci-dessous montre les circuits internes du CI. La couche bleue est la couche métallique supérieure de la puce, la couche verte est la couche de silicium inférieure. Carrés noirs autour du périmètre - 40 sites pour la communication avec les contacts externes du CI. J'ai utilisé ces photomasques pour faire de l'ingénierie inverse du processeur afin de comprendre ses circuits simples mais intelligents de type RISC.

Le nanoprocesseur est très similaire au processeur RISC (Reduced Instruction Set Computer), bien qu'il soit apparu plusieurs années avant un tel concept. En particulier, Nanoprocessor est conçu avec un système d'instructions simple, toutes les instructions sont exécutées en un cycle d'horloge (après l'horloge d'échantillonnage), le jeu de registres est grand et orthogonal, et l'adressage est simple. Ces caractéristiques inhérentes au RISC ont entraîné des vitesses d'horloge plus élevées par rapport aux processeurs plus complexes.

Le nanoprocesseur a été développé en 1974, en même temps que les processeurs classiques Intel 8080 et Motorola 6800. Cependant, le processus de fabrication du silicium Nanoprocessor a pris du retard de plusieurs années - ils ont utilisé des transistors à grille métallique au lieu du siliciumdéveloppé à la fin des années 1960. La différence semble déroutante, mais les portes en silicium étaient meilleures à plusieurs égards . Premièrement, ils sont plus petits, plus rapides et plus fiables. Deuxièmement, ils avaient une couche de silicium polycristallin avec des conducteurs autres que du métal; en conséquence, la disposition des puces était presque deux fois plus dense. Troisièmement, les transistors à grille métallique nécessitaient une alimentation supplémentaire de + 12 V. Le processeur Intel 4004 utilisait des portes en silicium en 1971, donc je suis surpris que HP ait encore utilisé du métal en 1974.

Compte tenu de ces limitations, je suis impressionné par la densité de câblage du nanoprocesseur - une couche de métal, pas de polysilicium. J'ai cherché d'autres puces à grille métallique et leur câblage est terriblement inefficace - il y a plus de conducteurs que de transistors. Dans le même temps, les chaînes de nanoprocesseurs sont localisées efficacement et ne gaspillent pas d'espace supplémentaire.

La technologie des nanoprocesseurs a dépassé Intel 8080 et Motorola 6800 en une chose: elle utilisait des transistors pull-up en mode d'épuisement, plus avancés que les transistors en mode d'amélioration utilisés dans les modèles 8080 et 6800. La première technologie fournit des portes logiques plus rapides et moins consommatrices, mais nécessitant une étape de production supplémentaire. Au nanoprocesseur, le masque photo n ° 3 (gris) a été utilisé dans cette étape. Des processeurs tels que le MOS Technology 6502 et le Zilog Z80, les transistors pull-up avec leur propre canal leur permettaient de fonctionner à une tension, pas trois. Malheureusement, le nanoprocesseur nécessitait toujours des tensions différentes en raison du transistor à grille métallique.

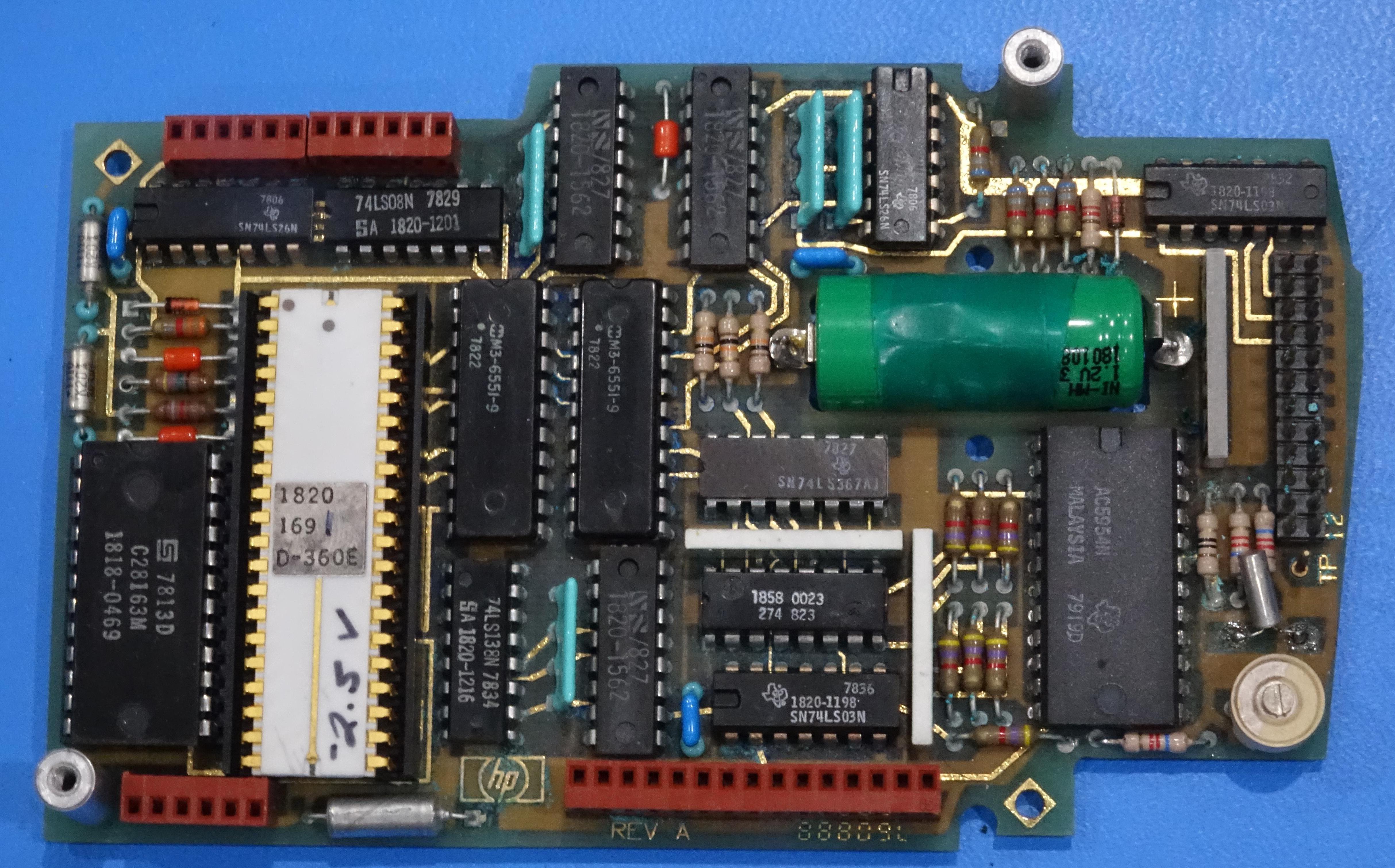

Une caractéristique très étrange du nanoprocesseur est la tension de polarisation alternative du substrat. Pour des raisons de vitesse, de nombreux microprocesseurs des années 1970 ont appliqué une tension négative au substrat de silicium, avec -5 V appliqué à travers le contact de polarisation. Le nanoprocesseur a une broche de polarisation, mais il est étrange que la tension de polarisation varie d'une puce à l'autre, de -2 V à -5 V. Pendant la production, la tension requise a été écrite sur la puce à la main (voir ci-dessous). Chaque nanoprocesseur devait être installé avec une résistance correspondante pour obtenir la tension correcte. Si le nanoprocesseur était changé sur la carte, la résistance devait également être changée. Le biais variable ressemble à un défaut de fabrication - je ne peux pas imaginer Intel faire cela dans les processeurs.

Les premières puces DRAM et microprocesseurs nécessitaient souvent trois tensions d'alimentation: +5 V (Vcc), +12 V (Vdd) et -5 V (Vbb) tension de décalage. À la fin des années 1970, les progrès de la technologie de fabrication ont permis d'utiliser une seule tension. Le microcontrôleur Intel 8080 de 1974 utilisait des transistors à canal induit qui nécessitaient trois tensions, mais une version améliorée du 8085 (1976) utilisait un transistor avec son propre canal et était alimenté par une seule tension de + 5 V. Depuis la fin des années 1970, de nombreux microprocesseurs ont utilisé des générateurs de pompe de charge. situé sur la puce pour générer une tension de polarisation négative.

Numéro de référence du nanoprocesseur HP 1820-1691. Notez la tension manuscrite: -2,5 V. Le dernier chiffre du numéro de pièce (1) est également manuscrit et représente la vitesse de la puce.

Comme la plupart des processeurs de cette époque, le nanoprocesseur était 8 bits. Cependant, il n'a pas utilisé de mémoire à accès aléatoire, mais a exécuté le code à partir d'une ROM externe de 2 Ko. Il avait 16 registres 8 bits - plus que la plupart des processeurs et suffisamment pour compenser le manque de mémoire dans de nombreuses applications. En termes de nombre de transistors, le nanoprocesseur est plus compliqué que Intel 8008 (1972) et légèrement plus facile que 6800 (1974) ou 6502 (1975).

D'après mes calculs, le nanoprocesseur a 4639 transistors. Le décodeur d'instructions est composé de paires de petits transistors basés sur des considérations d'emplacement. La combinaison de ces paires donne 3829 transistors uniques. Parmi ceux-ci, 1061 sont des pull-ups et 2668 sont actifs. A titre de comparaison, 6502 avait 4237 transistors, dont 3218 étaient actifs, le 8008 avait 3500 transistors, tandis que le Motorola 6800 en avait 4100.

Mais son architecture utilise des transistors dans un but différent de ces processeurs. Le nanoprocesseur n'a pas d'ALU, mais a à la place un grand ensemble de registres occupant la majeure partie de la zone de la puce. Le nanoprocesseur compte 48 équipes, nettement moins que les 6800 avec 72 équipes. Cependant, Nanoprocessor a des opérations pratiques de réglage, de réinitialisation et de vérification des bits que les processeurs mentionnés n'avaient pas. Le nanoprocesseur prend en charge l'accès aux registres par index, mais il n'a pas de modes d'adressage complexes comme les autres processeurs.

Les premiers microprocesseurs n'avaient pas d'opérations de définition de bits, de réinitialisation et de vérification (bien qu'elles puissent être implémentées via ET et OU). Le Z80 (1976) a ajouté des opérations au niveau du bit, mais elles étaient de deux octets chacune et étaient beaucoup plus lentes que Nanoprocessor.

Le schéma fonctionnel ci-dessous montre la structure interne du nanoprocesseur. La principale fonction d'E / S est la «Sélection de périphérique d'instruction d'E / S» 4 bits, qui permet à 15 périphériques de recevoir des commandes d'E / S. En d'autres termes, les broches sélectionnées déterminent quel périphérique d'E / S lit ou écrit à partir des bus de données. Les circuits externes utilisent ces signaux pour tout ce dont une application particulière a besoin - stocker des données dans un verrou, envoyer à un autre système, lire des valeurs. Encore plus d'E / S sont fournies via les broches d'E / S de contrôle direct (broches GPIO), adaptées à l'entrée et à la sortie. Si ces broches ne sont pas connectées à des circuits externes, elles agissent comme des indicateurs de bits de commodité; Le nanoprocesseur peut définir une valeur puis la lire.En l'absence de module logique arithmétique, le module logique de commande effectue des opérations d'incrémentation, de décrémentation, de décalage et des opérations de bit sur l'additionneur.

Schéma de principe du manuel d'utilisation du nanoprocesseur

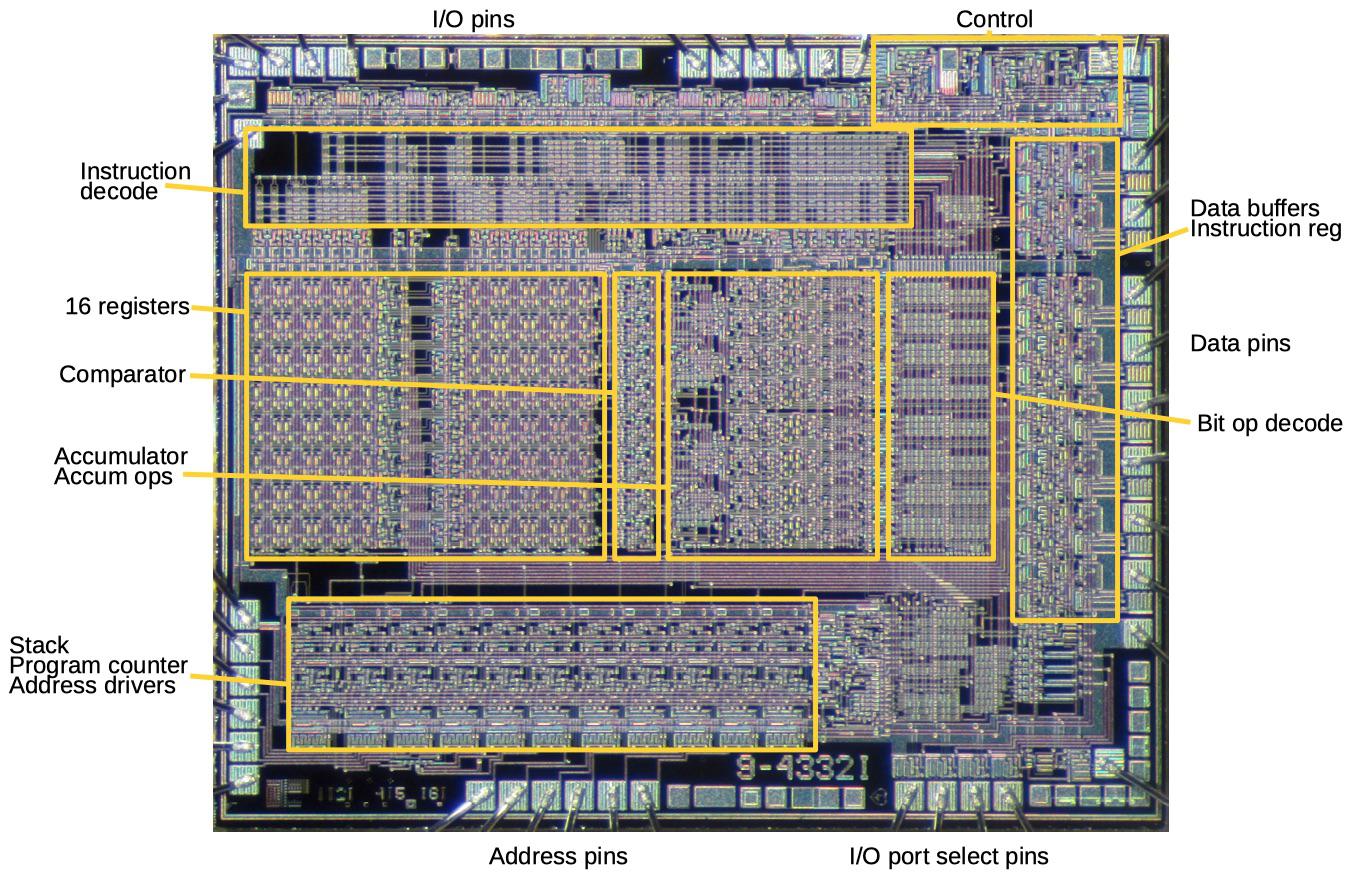

J'ai procédé à la rétro-ingénierie du nanoprocesseur basé sur des photomasques et cartographié le placement des blocs fonctionnels sur la matrice. Le plus gros élément est un ensemble de 16 registres à gauche du centre. Sur la droite se trouvent le comparateur et l'additionneur, ainsi que leurs circuits d'incrémentation, de décrémentation, de décalage et de complément. Le décodeur d'instructions occupe la majeure partie de l'espace au-dessus et à droite du comparateur de batterie. Le bas de la puce est principalement occupé par un compteur d'instructions de 11 bits, ainsi qu'une pile d'interruptions à entrée unique et une pile de sous-programmes. Les circuits de contrôle mettent en œuvre la synchronisation des commandes la plus simple: un cycle d'extraction est suivi d'un cycle d'exécution. La plupart des microprocesseurs ont des circuits de contrôle qui occupent une partie importante de la puce, mais les circuits de contrôle des nanoprocesseurs sont de petits blocs.

Le nanoprocesseur adhère à son modèle d'exécution des instructions en un cycle, même pour les instructions à deux octets: le deuxième octet est demandé pendant le cycle d'exécution, de sorte que le temps total d'exécution de la commande ne change pas.

Composants fonctionnels du nanoprocesseur HP

Comprendre les photomasques

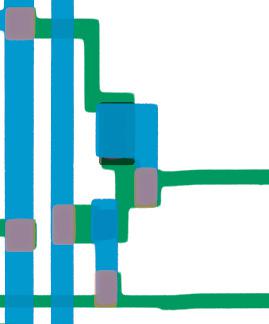

La puce a été fabriquée à l'aide de six photomasques, dont chacun a été utilisé pour produire l'une des couches de processeur par photolithographie . La photo ci-dessous montre des photomasques. Chacun est une feuille de Mylar de 47,2 x 39,8 cm. Ce sont des photomasques agrandis 100x utilisés pour produire un cristal de silicium de 4,72 x 3,98 mm (33% plus petit que le cristal de 6800). Chaque tranche de silicium de 3 pouces contenait environ 200 circuits intégrés, qui étaient produits simultanément, puis testés, coupés et placés dans un emballage.

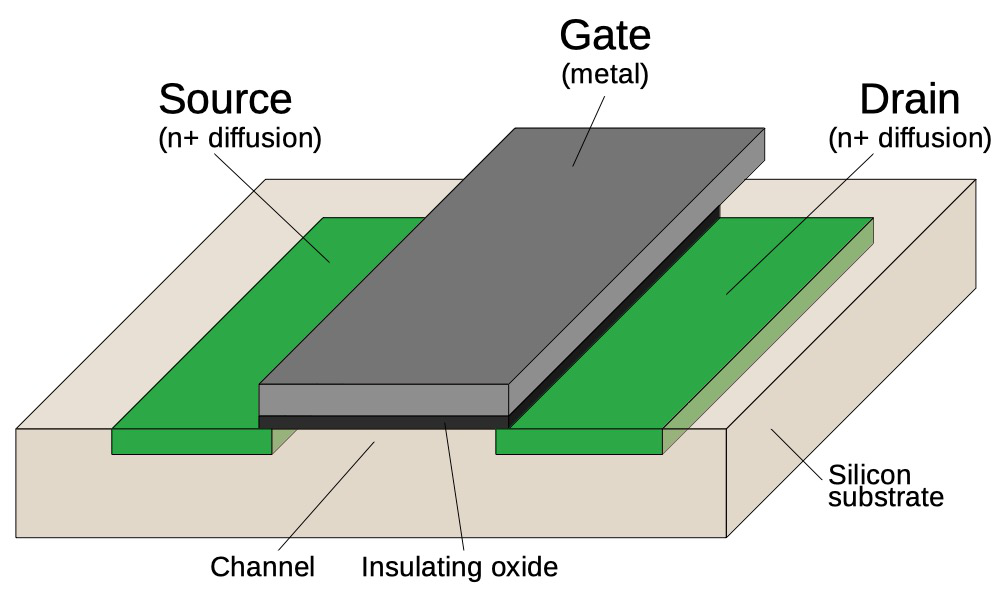

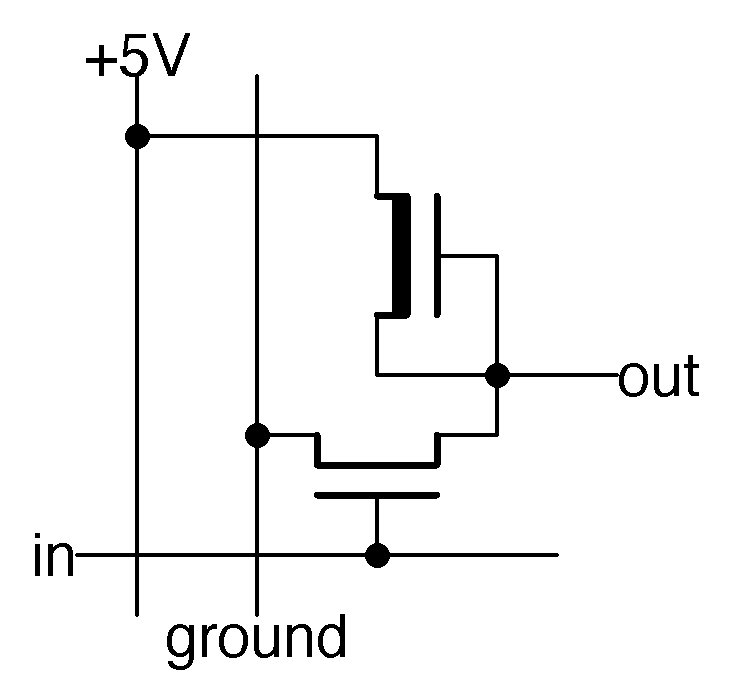

Pour expliquer le rôle des masques, je commencerai par décrire la structure MOS de la grille métallique utilisée dans le nanoprocesseur. Dans le schéma ci-dessous, deux sections de silicium (vert) sont rendues conductrices à l'aide d'impuretés, et forment la source et le drain du transistor. Une bande métallique entre eux forme une grille, séparée du silicium par une fine couche d'oxyde isolant (d'où le nom de la structure - métal, oxyde, semi-conducteur). Le transistor peut être considéré comme un interrupteur commandé par la grille. De plus, la couche métallique constitue le principal procédé de connexion des composants IC avec des conducteurs, bien que certains conducteurs traversent également la couche de silicium.

Schéma d'une structure MOS avec une grille métallique

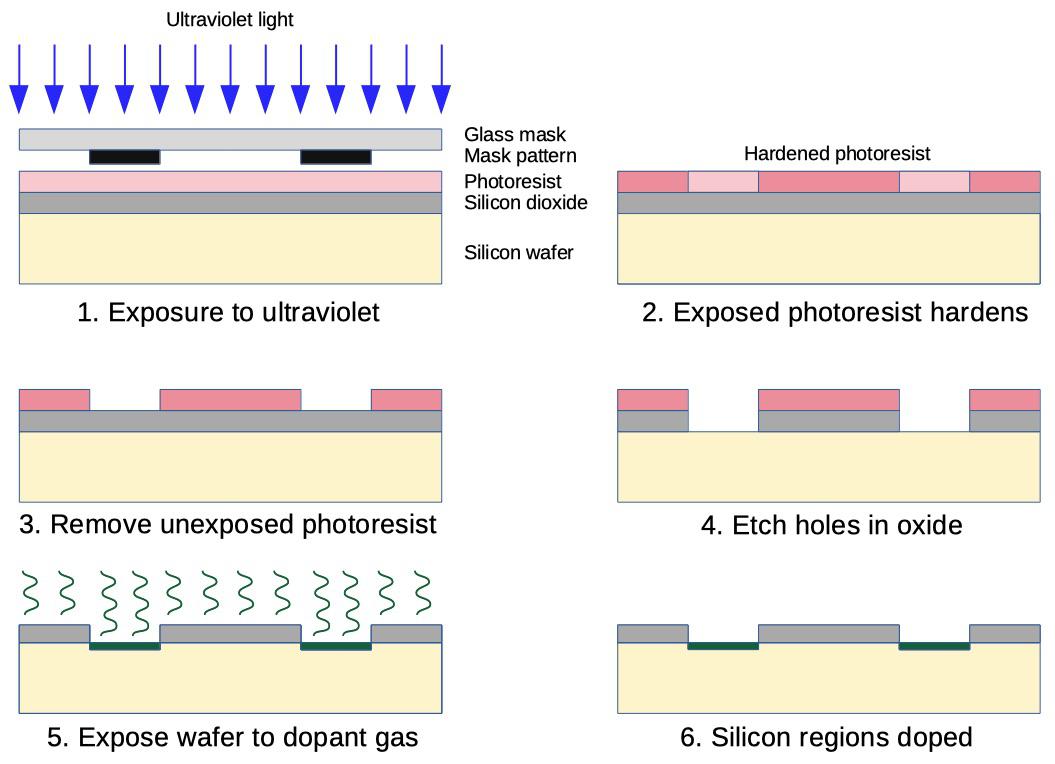

Les photomasques sont un élément clé du processus de fabrication des circuits intégrés car ils localisent les composants. Le diagramme ci-dessous montre comment les impuretés sont ajoutées à certaines zones de silicium à l'aide de photomasques. Tout d'abord, une couche d'oxyde isolant est formée sur le substrat de silicium, puis une résine photosensible est ajoutée.... La lumière ultraviolette (1) polymérise et durcit le photorésist partout sauf là où le masque bloque le passage de la lumière (2). Ensuite, le photorésist doux qui n'a pas été exposé au rayonnement ultraviolet est éliminé (3). Le substrat est exposé à l'acide fluorhydrique, qui enlève la couche d'oxyde là où elle n'est pas protégée par le photorésist (4). Des trous apparaissent dans l'oxyde qui correspondent au motif du photomasque. Ensuite, le substrat est exposé à un gaz chaud qui pénètre dans des zones non protégées de silicium et modifie ses propriétés conductrices (5). Ce processus génère de petites zones de silicium avec des impuretés, correspondant à l'image sur le photomasque (6). D'autres photomasques sont utilisés pour d'autres étapes de production, mais ils utilisent le même procédé utilisant un photorésist.

Comment les impuretés sont ajoutées aux régions de silicium à l'aide de photomasques Je vais

agrandir une section du nanoprocesseur pour montrer comment un circuit est formé à partir de six photomasques (qui est un inverseur qui change la valeur binaire fournie à l'entrée). En utilisant le premier photomasque et le processus de photolithographie décrit ci-dessus, les régions de silicium sont rendues conductrices. Les zones marquées en vert avec des impuretés formeront les sources / drains du transistor ou la jonction de composants.

Le premier photomasque crée des patchs de silicium conducteur

Le cristal est ensuite recouvert d'une couche d'oxyde isolante. Le deuxième photomasque (violet) est utilisé pour graver des trous dans l'oxyde qui exposent le silicium sous-jacent. Ces trous peuvent être utilisés pour créer les grilles du transistor ainsi que la connexion de conducteurs métalliques et silicium.

Le deuxième photomasque crée des trous dans la couche d'oxyde,

le troisième photomasque (gris) expose des zones d'implantation d'ions qui modifient les propriétés du silicium et, par conséquent, du transistor. Cela transforme le transistor supérieur en un transistor canalisé qui tire la sortie de la porte logique vers le haut.

Le troisième photomasque (gris) crée des impuretés dans le silicium du transistor supérieur

Le silicium est ensuite revêtu d'une fine couche supplémentaire d'oxyde isolant pour former les oxydes de grille du transistor. Le quatrième photomasque (orange) enlève cet oxyde des zones qui deviendront des contacts entre le silicium et la couche métallique. Après cette étape, la majeure partie du cristal est recouverte d'un oxyde isolant épais. Au-dessus des grilles du transistor (violet), la couche d'oxyde est très fine et présente des trous pour les contacts du photomasque actuel (orange).

Le quatrième photomasque crée des trous dans l'oxyde

Le cinquième photomasque (bleu) est utilisé pour créer des conducteurs métalliques sur le dessus - pour cela, une couche uniforme de métal est d'abord appliquée, et les parties inutiles sont ensuite gravées. Aux endroits où le quatrième masque a créé des trous dans l'oxyde, la couche métallique entre en contact avec du silicium et forme un contact conducteur. Là où le troisième masque a créé une couche mince d'oxyde, la couche métallique forme la grille du transistor entre les deux sections de silicium. Enfin, l'ensemble du substrat est recouvert d'une couche vitreuse protectrice. Le sixième photomasque est utilisé pour créer des trous dans cette couche au-dessus des contacts sur les bords de la puce. Après avoir découpé tout le substrat en cristaux individuels, une soudure par fil est soudée à ces contacts, les reliant aux contacts externes.

Le cinquième photomasque crée une disposition métallique

Le schéma ci-dessous montre comment ce circuit forme un onduleur à deux transistors. Les deux symboles du transistor correspondent aux deux transistors obtenus à l'aide du photomasque. En l'absence de signal d'entrée, le transistor supérieur (connecté à +5 V) tire la sortie vers le haut. Lorsque le signal d'entrée est haut, il active le transistor inférieur. Cela relie la prise à la terre, tirant la prise vers le bas. Ainsi, le circuit inverse le signal d'entrée.

Circuit onduleur N-MOS correspondant aux modèles ci-dessus

Bien que les schémas ci-dessus montrent un seul onduleur, ces étapes utilisent des photomasques pour créer un processeur complet avec les 4 639 transistors. Le schéma ci-dessous montre une plus grande partie de la puce, sur laquelle des dizaines de transistors forment des grilles et des circuits plus complexes. J'ai remarqué une chose touchante sur l'un des photomasques - un petit cœur avec les lettres HP à l'intérieur, sous le numéro de puce.

Le nanoprocesseur a deux numéros de référence différents. 1820-1691 désigne la version 2,66 MHz et 1820-1692 la version 4 MHz. Le dernier chiffre a été écrit manuellement sur chaque puce après avoir été vérifié dans le boîtier. Le numéro de pièce n'est pas lié au numéro de puce 9-4332A sur la matrice.

Dessins de puces

Comment le nanoprocesseur contrôle l'horloge

Pour comprendre comment le nanoprocesseur était utilisé dans la pratique, j'ai procédé à une ingénierie inverse du code du module d'horloge HP 98035. Le module était connecté à un ordinateur de bureau HP 9825 et servait d'horloge en temps réel, et pouvait également mesurer des intervalles et déclencher des événements périodiques avec une précision de la milliseconde. Le circuit du module d'horloge était plutôt inhabituel. Pour conserver l'heure actuelle lorsque l'ordinateur est éteint, le module d'horloge a été construit sur la base d'une puce d'horloge numérique avec une batterie de rechange. La puce d'horloge n'était pas conçue pour le contrôle par ordinateur, ce qui causait des inconvénients: elle générait des signaux à 7 segments pour contrôler les LED et était configurée avec trois boutons. Pour connaître l'heure, Nanoprocessor a dû convertir la sortie de l'affichage à 7 segments en nombres.Pour régler l'heure du nanoprocesseur, vous deviez émuler la séquence correcte de pressions sur les boutons.

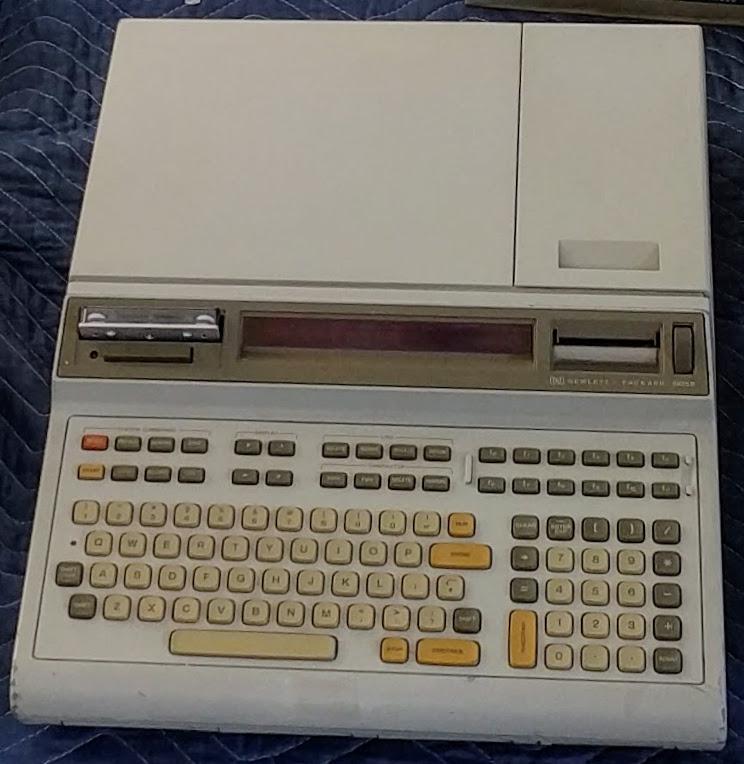

Le HP 9825 était un ordinateur de bureau 16 bits prenant en charge un langage similaire à BASIC. Introduit en 1976, cinq ans avant l'IBM PC, c'était un système assez avancé pour l'époque. À l'arrière, il y avait trois connecteurs pour ajouter des modules tels qu'un module d'horloge en temps réel.

HP 9825 avec écran LED, lecteur de bande et imprimante

Pour économiser de l'énergie, la puce d'horloge de Texas Instruments est implémentée sur une logique d'injection intégrée (I2L). Les puces de faible puissance aujourd'hui utiliseraient CMOS, mais c'était rare à l'époque. I2L a été construit sur des transistors bipolaires, similaires au TTL, mais utilisant différents circuits à haute densité et à faible consommation d'énergie. C'était peut-être une puce X-902 dans un boîtier DIP.

Nanoprocesseur (puce blanche) faisant partie du module d'horloge HP. À gauche se trouve une ROM de 2 Ko. Sur la droite se trouvent deux puces de mémoire 256 bits x 4. La puce d'horloge Texas Instruments est une grosse puce noire sous la batterie NiCad verte.L'ordinateur

contrôlait le module d'horloge en lui envoyant des chaînes ASCII de caractères comme "S 12: 07: 12: 45: 00", ce qui aurait dû régler l'heure à 12:45:00 7 décembre (ou 12 juillet en notation européenne). Les différents compteurs d'intervalles, alarmes et compteurs du module ont été initiés de manière similaire, par des commandes telles que "Unit 2 Period 12345". Le module a pris en charge 24 commandes, et le nanoprocesseur devait les reconnaître .

Voici un morceau de code rétro-ingénierie à partir de la ROM de la carte d'horloge. Il s'agit du code du gestionnaire d'interruption qui incrémente le minuteur et la date toutes les secondes. Le code détermine le nombre de jours dans un mois afin qu'il sache quand changer le mois au suivant. Colonnes - valeurs d'octets, commandes et mes explications. Ce code récupère le numéro du mois (01-12 BCD), le stocke dans l'accumulateur et renvoie le nombre de jours du mois (28, 30 ou 31 BCD) dans le registre 0. Pas mal pour 16 octets de code, malgré l'ignorance des années bissextiles. Comment ça marche? Pendant des mois après le 7 (juillet), il soustrait 1. Ensuite, si le mois est impair, il a 31 jours, et s'il est pair, 30 jours. Pour traiter février, le code efface le bit 1 mois. Si le mois devient 0 (février), alors il a 28 jours.

d0 STR-0 (7) 0.

07

0c SLE , <= 0.

03 DED 1

5f NOP

d0 STR-0 (0x31) 0

31

30 SBZ-0 , 0 0

81 JMP-1 0x1c9 ( )

c9

a1 CBN-1 1

d0 STR-0 (0x30) 0

30

0f SAN , 0

d0 STR-0 (0x28) 0

28

Vous pouvez voir à partir du code que même si un processeur sans opération d'addition semble inutile, les opérations au niveau du bit et l'incrémentation / décrémentation du nanoprocesseur permettent plus de calculs que vous ne le pensez.

Dans le code, je suis tombé sur un endroit où je dois ajouter deux numéros BCD et former un octet. Cela a été fait par un cycle qui a diminué un nombre et augmenté un autre. Lorsque le premier nombre a atteint zéro, le second a obtenu leur somme. Ainsi, même sans ALU, l'addition peut être effectuée, quoique lentement.

Vous pouvez également voir que le code du nanoprocesseur est compact et efficace. Vous pouvez faire beaucoup de choses dans un octet, ce qui dans d'autres processeurs prend plusieurs octets. Un grand nombre de registres de nanoprocesseurs vous permet d'éviter un échange de données morne. Alors que certains considèrent que le nanoprocesseur est plus une machine à états qu'un microprocesseur, ce serait une sous-estimation des capacités et du rôle du nanoprocesseur.

Bien que le nanoprocesseur ne dispose pas d'ALU ou de commandes de mémoire à accès aléatoire, ils peuvent être connectés en tant que périphériques d'E / S supplémentaires. La montre dispose d'une mémoire vive de 256 octets qui stocke les valeurs des compteurs et des minuteries, dont l'accès est organisé via les ports d'E / S. D'autres produits ont ajouté des ALU pour prendre en charge les opérations arithmétiques.

Le diagramme de la carte d'horloge montre comment deux puces de RAM 256x4 sont connectées au nanoprocesseur. Le port E / S du nanoprocesseur sélectionne une broche et se connecte au «3-8 Decoder» U5, qui émet des signaux séparés pour chacun des ports E / S. Trois d'entre eux vont aux broches de contrôle de la puce RAM, et un contrôle les puces des verrous de données U9 et U10, qui contiennent les données écrites.

Tous les ports d'E / S utilisent le bus de données du nanoprocesseur (en haut) pour échanger des données, de sorte que le bus se connecte à la fois aux broches d'adresse des puces de RAM et aux broches de données. Pour la lecture, l'adresse mémoire est écrite sur les puces via un port d'E / S, puis les données sont lues depuis la mémoire via un autre port. Dans les deux cas, les valeurs transitent par le bus de données et le signal du "3-8 Decoder" indique ce qu'il faut faire avec les valeurs. Pour l'écriture, la première opération d'E / S stocke la valeur d'octet dans les verrous, puis la deuxième opération d'E / S envoie l'adresse aux puces de mémoire. Cela peut sembler une approche maladroite du style machine Goldberg , mais en pratique, cela fonctionne bien et la lecture / écriture peut être effectuée avec deux octets d'instructions.

De nombreux processeurs, tels que le 6502, utilisent des E / S mappées en mémoire - les périphériques sont mappés à l'espace d'adressage mémoire et accessibles via des opérations de lecture / écriture. Le nanoprocesseur fonctionne dans l'autre sens, en branchant la mémoire dans un port d'E / S et en y accédant via des opérations d'E / S.

Lors de l'ajout d'ALU, une approche similaire est utilisée- comme dans le voltmètre HP 3455A utilisant deux nanoprocesseurs. Le voltmètre utilise deux puces 74LS181 ALU pour implémenter une ALU 8 bits, qu'il utilise pour mettre à l'échelle les valeurs et calculer le pourcentage d'erreur. Deux ports de sortie fournissent des arguments et un définit une opération. Le résultat 8 bits est lu depuis le port, et le processeur lit le transfert via la broche GPIO (on se demande s'il était plus facile d'utiliser un processeur avec support arithmétique).

Résultat

Le nanoprocesseur est un processeur inhabituel. À première vue, il m'a même semblé un "faux processeur", en raison du manque d'opérations arithmétiques de base. La puce est basée sur une technologie de grille métallique obsolète qui a traîné derrière d'autres microprocesseurs pendant plusieurs années. Le plus étrange est que chaque puce nécessite sa propre tension, qui a été écrite manuellement sur le boîtier, ce qui indique les difficultés avec une qualité stable en production. Cependant, le nanoprocesseur dans le rôle d'un microcontrôleur a fonctionné rapidement, beaucoup plus rapidement que les autres processeurs modernes. Hewlett-Packard a utilisé le nanoprocesseur dans de nombreux produits dans les années 1970 et 1980, dans des rôles plus sophistiqués qu'on ne pouvait s'y attendre.

Bien que le nanoprocesseur ait longtemps été oublié, et même pas évoqué sur Wikipédia, les photomasques récemment publiés par son créateur mettent en lumière ce coin inhabituel de l'histoire des processeurs.