Les

périphériques de mémoire non volatile (NVM) Intel / Micron NAND Flash Chip sont des périphériques de stockage électroniques de lecture et d'écriture qui continuent de stocker des informations après une panne de courant. Il s'agit notamment de dispositifs basés sur des disques magnétiques et de certains types de puces semi-conductrices. Les appareils semi-conducteurs non volatils jouent un rôle important dans tous les aspects de l'univers numérique - des cellules de stockage d'énormes banques de données dans le cloud aux appareils personnels portables - et constituent l'un des segments les plus importants de l'industrie des semi-conducteurs de 400 milliards de dollars.

Comme tout produit semi-conducteur important, du transistor au microprocesseur, les dispositifs NVM ont parcouru un long chemin depuis le travail des premiers explorateurs qui ont pris le travail de leurs prédécesseurs comme base et les ont développés grâce à l'inspiration, la chance, les essais et erreurs, ainsi que la détermination d'ignorer les doutes des sceptiques. Dans cet article, nous partageons par ordre chronologique certains de ces pionniers et leurs contributions, depuis les débuts d'une idée en 1960 chez Fairchild jusqu'à la production à grande échelle de puces flash dans la dernière décennie du 20e siècle.

Au nom du Semiconductor Special Interest Group (SIG), Jeff Katz a enregistré des entretiens avec des contributeurs au développement de dispositifs commerciaux à semi-conducteurs NVM pour la Oral History CollectionMusée d'histoire de l'informatique. Bon nombre des commentaires personnels cités ci-dessous sont tirés de transcriptions d’entrevues, auxquelles on peut accéder via les liens dans le texte.

Avant la mémoire non volatile à semi-conducteur

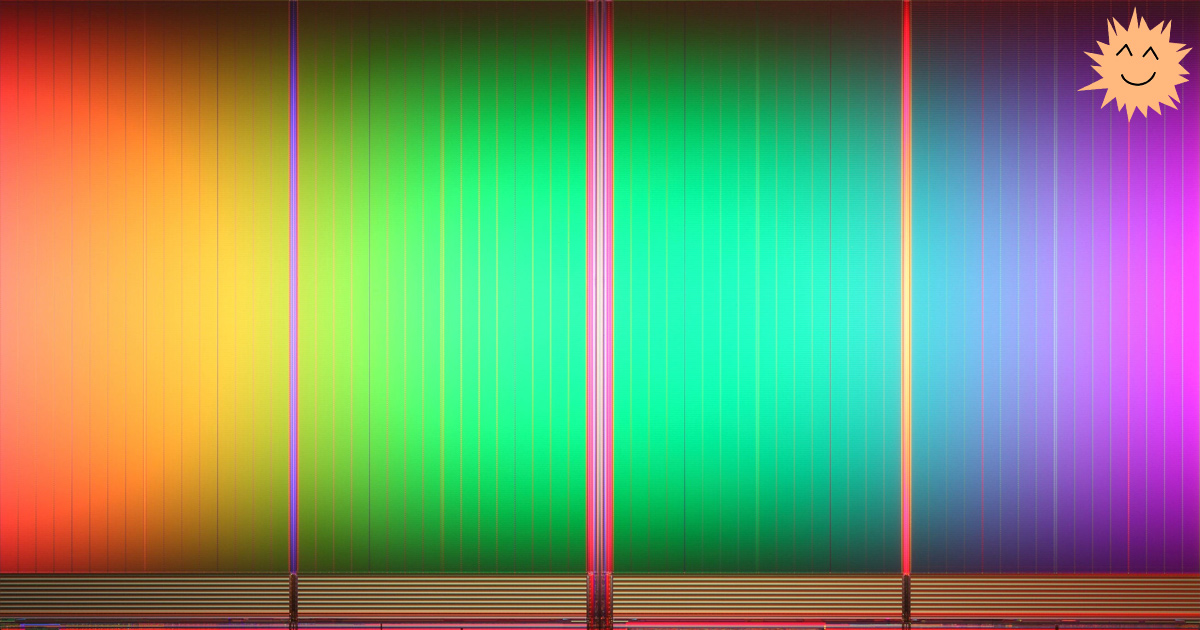

Avant l'avènement des dispositifs à semi-conducteurs, la technologie la plus réussie pour le stockage informatique non volatile était la mémoire à noyau magnétique, qui utilisait l'effet de l'hystérésis magnétique. Dans sa thèse1952 pour son doctorat au MIT, Dudley Buck a décrit des cristaux ferroélectriques qui utilisaient un mécanisme d'hystérésis similaire pour stocker et magnétiser les informations numériques. Reid Anderson et Walter Merz de Bell Telephone Laboratories ont démontré en 1955 le dispositif de stockage ferromagnétique qui était le précurseur de l'architecture des semi-conducteurs NVM. En utilisant des technologies de dépôt et de gravure, ils ont fabriqué un réseau de 256 bits de cristaux reliés par des chemins métalliques; plus tard, ces technologies ont commencé à être appliquées à la production de circuits intégrés à semi-conducteurs.

Photo du magazine Scientific American , juin 1955.

Larry McMillan et George Rohr, fondateurs de Ramtron, basés à Colorado Springs, ont été les pionniers de la commercialisation des dispositifs de mémoire à accès aléatoire ferroélectrique (FRAM) , introduits pour la première fois en 1952.

Évolution de la technologie cellulaire NVM - Les quatre premières décennies

Dans les années 1960, des recherches ont commencé sur les deux principales technologies de conception de cellules NVM à semi-conducteurs. Dans une cellule «à grille flottante», la charge est stockée sur une électrode qui n'est pas connectée à un circuit externe. Le «piégeage de charge», le plus souvent appelé «piégeage de nitrure», permet de stocker une charge dans une couche de nitrure de silicium reliée à un circuit actif. Les deux technologies promettaient des avantages significatifs et des coûts de fabrication réduits, une facilité d'utilisation et une rétention des données pour une variété d'applications.

Des composants et des systèmes commerciaux utilisant les deux technologies ont commencé à émerger dans les années 1970. Les produits basés sur la capture de charge étaient le plus souvent appelés EAROM (mémoire morte électriquement effaçable), et les premiers dispositifs à grille flottante étaient appelés EPROM (Erasable Programmable ROM).

Dans les années 1980, la mémoire à obturateur flottant était devenue la technologie dominante sur le marché. Les EPROM et leurs améliorations, y compris les premiers produits flash, sont devenues un pourcentage important des bénéfices de l'industrie mondiale des semi-conducteurs. Dans les années 1990, la technologie Flash a fourni de nouvelles opportunités pour les périphériques NVM, et ils ont commencé à être utilisés dans les disques SSD et les périphériques numériques grand public.

1960 - pionniers de l'élément mémoire

Sa Zhitan, vers 1989

Sa Zhitan du laboratoire de recherche Fairchild à Palo Alto a rapporté en 1961 qu'une charge pouvait être stockée "pendant une longue période (plusieurs jours)" à l'électrode de grille d'un MOSFET à tétrode contrôlé en surface. Il a noté que dans une conversation avec le fondateur de Fairchild Victor Greenich et l'ingénieur Frank Wanless, ils "ont immédiatement compris le potentiel de cette découverte dans un dispositif de mémoire à obturateur flottant." Ils n’ont pas proposé d’idée de produit car la société était alors occupée à résoudre les problèmes de stabilité fondamentaux du processus MOSFET.

Les premières descriptions documentées des cellules de mémoire à capture de charge ont été créées dans des laboratoires sur les deux côtes des États-Unis au milieu des années 1960. Edgar Sack, Chu Tinh et d'autres du Westinghouse Central Research Laboratory ont utilisé la structure métal-nitrure-oxyde-silicium (MNOS) en 1966 comme élément de piégeage de charge³. Chu et John Scedon ont parlé de l'élément Westinghouse MNOS lors de la conférence de recherche sur les dispositifs à état solide de 1967 à Santa Barbara. Cette technologie a été transférée à la division semi-conducteurs de la société à Youngwood pour développer des fusibles d'artillerie électroniques destinés à remplacer les fusibles mécaniques.

Zone propre de la division des semi-conducteurs de Westinghouse à Youngwood, vers 1959. Photo par E. Sack

Dans le même 1967, six scientifiques dirigés par Richard Wegener du Sperry Rand Research Center (Sudbury, Massachusetts) ont décrit un dispositif de stockage MNOS indestructible électriquement programmable avec capture de charge. Dans un rapport de la NASA de 1968, "A Study of New Concepts for Adaptive Devices", Wegener a déclaré que le MNOS est "le premier dispositif à semi-conducteurs à fournir des capacités de stockage non volatiles électriquement programmables".

Dov Frohman-Benczkowski a rejoint le laboratoire de recherche Fairchild à Palo Alto en 1965. En tandem, il a rédigé son doctorat sur "Transfert de charge et piégeage dans les structures MNOS et leur application dans les dispositifs de mémoire" à l'Université de Californie à Berkeley, où "il en savait plus sur ce sujet que la plupart des professeurs". [ Entretien avec Dov Frohman ] . Sur la base de son travail, il a entamé le processus de demande de brevet, qui a été enregistré après avoir quitté l'entreprise. La demande de brevet comprenait une structure de masque pour créer une mémoire mot par mot MNOS 9 bits, qu'il a fabriquée pour démontrer les capacités des baies de stockage intégrées à grande échelle⁶.

Dawon Kang et Simon Zee

En étudiant un gâteau au fromage à quatre couches à l'heure du déjeuner au Bell Telephone Laboratories (BTL) en 1967, Murray Hill, Dawon Kang et Simon Zee ont eu l'idée d'ajouter une quatrième couche flottante pour stocker la charge dans le MOSFET. Pour prouver la viabilité du concept, ils ont fabriqué une douzaine d'appareils en laboratoire. "Les appareils ont duré au maximum une heure, après quoi les électrons ont commencé à fuir" [ Entretien avec Simon Zee ]... «Mon patron a dit que c'était complètement inutile ... Qui bénéficierait d'un tel appareil?», Dit Zee. Ils ont été autorisés à publier leur travail dans le journal de juillet 1967 "Floating Shutter and Its Applications in Memory Devices" dans le Bell System Technical Journal, mais BTL n'a pas poursuivi l'idée. "Ils l'ont juste mis sur l'étagère."

RMM 256 bits sur semi-conducteurs amorphes ECD / Intel, 1970

De nombreuses inventions et entrepreneur Stanford Ovshinsky ont fait sensation dans la communauté scientifique, déclarant en 1968 dans le New York Timesà propos de la création d'un commutateur avec une mémoire basée sur les éléments d'Ovshinsky. Cet appareil, développé dans son laboratoire de dispositifs de conversion d'énergie (ECD) à Troy, Michigan, utilisait des matériaux à base de chalcogénure non cristallin pour créer un interrupteur qui s'allumait ou s'éteignait lorsque la tension appliquée atteignait une certaine valeur. Ovshinsky a déclaré qu'il serait en mesure de produire des circuits électroniques plus petits, plus rapides, plus simples, plus fiables et moins chers que ce qui serait possible avec des transistors. L'étudiant à la maîtrise Charles Xi, qui a travaillé sur le changement à ECD, a déclaré que le principal avantage de la technologie est que "les informations peuvent être stockées pour toujours (pas de limite de temps pour la conservation des données)". [ Entretien avec Charles C. ]

Peu de temps auparavant, les fondateurs d'Intel, Robert Noyce et Gordon Moore, se sont associés à Ovshinsky pour étudier la technologie de création de mémoire non volatile afin de compléter leur propre future RAM basée sur des bipolaires et des MOSFET. Un article de 1970 de Gordon Moore, Ron Neil et D. Nelson de ECD décrit une mémoire à lecture la plus importante (RMM) de 256 bits constituée d'un film de matériau semi-conducteur amorphe pris en sandwich entre deux électrodes de molybdène. Intel s'est limité à cette démonstration du concept et n'a pas développé de produits basés sur celui-ci, cependant, il a renaître comme base de la mémoire à changement de phase 3D XPoint, qu'Intel et Micron ont annoncé en 2015; Intel a vendu des produits finis sous la marque Optane.

1970 - l'émergence des produits industriels NVM

Module multipuce Westinghouse BORAM, vers 1975.

Au début des années 1970, les dispositifs de mémoire MNOS non volatiles se sont révélés être un choix attrayant pour les concepteurs de systèmes aérospatiaux et de défense. L'US Air Force a attribué à Sperry Rand un contrat pour la construction d'une matrice EAROM de 1024 bits, et Westinghouse a conçu des modules hybrides de RAM orientée bloc (BORAM) électriquement reprogrammables pour l'armée américaine et d'autres clients. Plusieurs puces situées sur un substrat en céramique assuraient des avions et des systèmes portables légers et compacts.

Passant chez Intel en 1969, Dov Frohman a poursuivi ses recherches sur les technologies de stockage MNOS. Cependant, tout en étudiant les problèmes de stabilité causés par la migration de charge dans le nouveau processus de fabrication de grille en silicium de l'entreprise, il a proposé une autre idée de stockage de la charge dans un conducteur à grille flottante. "C'était une évolution de ce que j'ai appelé le dispositif FAMOS (Floating-gate Avalanche-injection Metal Oxide Semiconductor) ... qui était l'épine dorsale de l'EPROM." [ Entretien avec Dov Frohman ] Avant de déposer un brevet d'architecture, il ne connaissait pas le travail de Kang et Zee chez Bell Labs.

Dov Frohman-Benczkowski, vers 1971. Photo: Intel Corporation

Frohman a arrêté les travaux supplémentaires sur le lecteur MNOS pour se concentrer sur la conception d'un produit à grille flottante, et en 1971, Intel a présenté son EPROM 2048 bits, étiquetée 1702. Les EPROM étaient programmées électroniquement, mais l'effacement et la refonte l'utilisation n'a été possible qu'après traitement physique de la puce avec un rayonnement UV à travers une fenêtre en quartz dans le boîtier. Les versions moins chères et programmables une fois (OTP) qui ne nécessitaient pas de fenêtre d'effacement coûteuse se sont avérées populaires dans les systèmes à microprocesseur (MPU). Plusieurs générations d'EPROM plus grandes et plus rapides ont constitué la gamme de produits Intel la plus rentable jusqu'au milieu des années 1980.

La fenêtre en quartz transmet un rayonnement ultraviolet pour effacer les données EPROM

Les fabricants japonais de semi-conducteurs ont rapidement reconnu le potentiel commercial des EPROM. Le pionnier des circuits intégrés Yasuo Tarui du Tokyo Electrotechnical Laboratory et ses collègues ont proposé un dispositif à grille flottante en 1971 lors de la conférence Solid State Device⁸ à Tokyo. Cela a été suivi de nombreux articles de recherche et de produits commerciaux à succès d'entreprises japonaises.

Manuel EAROM de GI, 1983

En 1969, Ed Sack quitta Westinghouse pour General Instrument Corporation à Hicksville, NY. Il y a occupé le poste de vice-président et de directeur général de la division Microélectronique, qui a été le pionnier de la commercialisation de la technologie MNOS dans l'électronique grand public. Sa comparaison de Westinghouse ("Gentlemen's Club avec un Dash of Politics") et GI ("Manhattan's Lower East Side avec un Dash of Street Fighting") démontre les différences culturelles significatives entre les entreprises militaires et commerciales de semi-conducteurs de l'époque. [ L'histoire personnelle d'Ed Sack ]

En 1975, GI a introduit le ER1400 Bit-Serial EAROM, qui a été complété par un microprocesseur 16 bits CP1600 (co-développement avec Honeywell); ces produits visaient le chipset tuner TV numérique à semi-conducteurs et se sont vendus par millions. GI a continué à produire des dispositifs EAROM bon marché pour les produits de consommation pendant plusieurs décennies.

Parmi les autres fabricants qui ont étudié les technologies de mémoire non volatile MNOS, mentionnons McDonnell Douglas, Mitsubishi, NCR et RCA. Cependant, la croissance rapide du nombre d'appareils et la baisse des prix, entraînés par une concurrence intense dans les produits à grille flottante, ont fait d'EPROM la solution non volatile préférée pour la plupart des applications.

Des améliorations telles que la fonction d'effacement électrique ont encore renforcé la position des dispositifs à volet flottant. Eli Harari de Hughes Microelectronics (Newport Beach, Californie) En 1976 a eu l'idée "qu'il est possible de réduire la couche d'oxyde de grille dans le dispositif Frohman-Bentschkovski de 1000 angströms à 100 angströms pour fournir la programmation électrique et l'effacement" loin de la nécessité d'un effacement externe lent avec un rayonnement ultraviolet. [ Entretien avec Eli Harari ] En 1980, Hughes a introduit une PROM 8KBE électriquement effaçable (EEPROM), étiquetée 3108, et une puce SRAM non volatile appelée NOVRAM.

George Perlegos

George Perlegos a contribué à plusieurs développements NVM importants chez Intel, y compris le premier EEPROM: l'appareil 16K 2816 créé en 1978. Avec Gordon Campbell et Phil Salisbury, Perlegos a fondé SEEQ Technology en 1981. Dans cette société, Perlegos a dirigé le développement du 5213, une seule EEPROM de 5 volts lancée en 1982, dans le but d'éliminer le besoin d'une alimentation haute tension séparée. Sa conception comprenait une pompe de charge qui génère la tension requise pour prendre en charge la programmation. "Pour créer ce type de mémoire, nous devions concevoir des pompes de charge si petites qu'elles pouvaient tenir dans chaque colonne et dans chaque ligne." [ Entretien avec George Perlegos] Pour encourager l'utilisation de ses appareils dans des applications exigeant une grande fiabilité, SEEQ les a annoncés comme capables de supporter au moins un million de cycles d'écriture.

Raphael Klein, ancien ingénieur des procédés nationaux pour les semi-conducteurs, a fondé Xicor en 1978 à Milpitas, en Californie, pour se concentrer sur les dispositifs NOVRAM et EEPROM. Dans un premier temps, Xicor partageait la croissance du marché naissant avec SEEQ, mais incapable de faire face à la concurrence dans la production d'appareils de masse à bas prix, il a terminé ses travaux en 2001.

1980 - l'émergence de l'architecture Flash

En 1980, Fujio Masuoka du centre de recherche et développement Toshiba de Kawasaki, au Japon, a embauché quatre ingénieurs: M. Asano, H.Iwahashi, T.Komuro et S.Tanaka pour travailler sur une puce NVM destinée à être utilisée dans des appareils de masse à faible coût. Les EPROM existantes utilisaient deux transistors par cellule mémoire. Les ingénieurs ont conçu une cellule à transistor unique plus compacte, connectée d'une manière similaire à la porte NOR. Le collègue de Masuoki, Shoji Ariizumi, a suggéré le nom de «flash» car l'effacement devait se produire à la vitesse d'un flash d'appareil photo. Masuoka a parlé de la cellule NOR Flash lors de la réunion internationale de 1984 sur les dispositifs électroniques (IEDM) tenue à San Francisco. Bien qu'il ait réussi à réduire la taille des cellules,en raison de problèmes de production de la structure MOS avec trois couches de silicium polycristallin nécessaires pour le dispositif, Toshiba n'a pas mis en œuvre la version commerciale de l'invention.

Selon Harari, Satyen Mukherjee et Thomas Chan de la startup Exel Microelectronics, Inc. (San Jose, Californie) Conçu une structure flash qui pourrait être fabriquée industriellement; il est devenu la base de ce que Intel a appelé plus tard le flash NOR.

Fujio Masuoka

En arrivant à Washington pour défendre une société dans un litige de brevet avec TI, Masuoka a eu l'idée d'une architecture NAND Flash qui pourrait fournir des tailles de cellules encore plus petites et des vitesses d'écriture / effacement plus rapides que NOR Flash. À son retour, Masuoka a demandé à Hiseo Tajiri, responsable du développement de l'électronique grand public chez Toshiba, si un appareil photo numérique doté d'un flash NAND de quatre mégabits pouvait remplacer le film. [ Entretien avec Fujio Masuoka ] Tajiri s'est rendu compte que NAND pouvait effectivement remplacer le film, ce qui a conduit le département de la caméra à financer le projet. Masuoka a parlé de l'appareil sur l'IEDM de 1987 à Washington DC, et la production de puces NAND Flash 16Mbit a commencé en 1992.

Malheureux que Toshiba, à son avis, n'ait pas suffisamment récompensé son travail, Masuoka a quitté son emploi en 1994, devenant professeur à l'université de Tohoku. Contrairement à la culture de loyauté japonaise de l'entreprise, il a intenté une action en justice contre son ancien employeur et a réglé le différend en 2006 pour une somme forfaitaire de 87 millions de yens (758 000 $).

Stefan Lai a rejoint le département Intel de Santa Clara pour développer la technologie EEPROM évolutive. En collaboration avec Dick Pashley, il a imaginé un moyen d'ajouter une fonctionnalité d'effacement électrique aux petites cellules EPROM préexistantes pour créer une architecture NOR Flash qui pourrait être fabriquée à l'aide d'un processus de fabrication standard. NVM a déclaré que la technologie ne fonctionnerait pas, alors Lai et Pashley ont rencontré Gordon Moore, qui leur a dit: "Je vais y arriver, ne vous inquiétez pas." [ Entretien avec Intel Flash ] Après avoir commencé le développement d'un nouvel appareil professionnel basé sur Flash à Folsom, en Californie, Pashley et Lai, avec le designer Niles Kynett, ont fait une démonstration de puces fonctionnelles en 1986 et ont sorti le produit NOR Flash de 256 kilobits en 1987. ...

À la fin des années 80, le marché mondial des dispositifs NVM à semi-conducteurs de toutes les technologies de fabrication dépassait 2 milliards de dollars. Les produits les plus populaires de cette époque étaient les EPROM 64Kbps, 128Kbps, 256Kbps et 1Mbps, et les premiers appareils 2Mbps ont commencé à apparaître. Les fabricants américains, menés par AMD, Intel, Motorola, SEEQ et TI, ont reçu environ 50% des bénéfices du marché mondial. Le reste du bénéfice a été réparti entre les fournisseurs européens, principalement SGS-Thompson (10%), et les fournisseurs japonais Fujitsu, Hitachi, Mitsubishi, NEC, Oki, Toshiba (40%), mais leurs approvisionnements étaient limités par les quotas de production gouvernementaux (MITI).

Années 1990 - Disques SSD et nouvelles applications grand public

Dans les années 90, la technologie Flash a créé de nouvelles possibilités pour les périphériques NVM dans les configurations NAND et NOR. L'architecture NOR Flash avait les avantages d'un accès aléatoire et de temps de lecture rapides, et sa fonction d'exécution sur place (XIP) était idéale pour l'exécution de code, et donc pour le traitement des données. NAND Flash avait des vitesses de lecture plus lentes mais une taille de cellule beaucoup plus petite, permettant des périphériques à faible coût et haute densité, idéaux pour le stockage externe. De plus, l'accès en lecture / écriture aux blocs NAND permet de simuler l'accès aux lecteurs de disque.

Prototype SSD SanDisk (anciennement SunDisk) pour IBM (1991)

Eli Harari, pionnier des processus d'oxyde mince chez Hughes Aircraft dans les années 1970, a fondé SunDisk (plus tard rebaptisé SanDisk) en 1988 pour développer des dispositifs de mémoire haute capacité basés sur une mémoire flash. Il fut bientôt rejoint par les cofondateurs Jack Yuan et Sanjay Mehrotra, et l'architecte système Robert "Bob" Norman. La première commande majeure de la société était de 10000 périphériques ATA plug-and-play de 20 Mo de 2,5 pouces pour remplacer le disque dur 20 Mo Connor du PC ThinkPad d'IBM en 1991. À l'époque, la fiabilité de la mémoire flash était faible, mais Harari était encouragé par les commentaires des clients sur les appareils prototypes: «Si plusieurs appareils fonctionnent correctement pour moi tout le week-end, vous avez un bon produit. [ Entretien avec Eli Harari]

Plusieurs générations d'améliorations du processus de fabrication et de l'architecture des systèmes de mémoire flash ont été nécessaires pour atteindre les niveaux de fiabilité requis pour les applications commerciales. Harari a intégré des métadonnées dans les appareils qui permettaient à son micrologiciel de corriger les erreurs, cachant ainsi à l'utilisateur les problèmes de fiabilité essentiels à la popularité de la technologie. Les ordinateurs portables grand public équipés de SSD sont arrivés sur le marché à la fin des années 2000, et les SSD modernes sont le segment du marché du stockage informatique qui connaît la croissance la plus rapide.

Fondateurs de SanDisk: Yuan, Mehrotra et Harari

SanDisk a une nouvelle opportunité après l'introduction des cartes CompactFlash pour appareils photo numériques en 1994. «Nous avons réalisé qu'au lieu de vendre des vendeurs de films ou d'appareils photo par quelqu'un d'autre, nous devions créer un marché secondaire pour les cartes flash. Sa transformation en une marque internationale a marqué un tournant dans l'histoire de l'entreprise », déclare Mehrotra. [ Entretien avec Sanjay Mehrotra ] En 2016, SanDisk a été racheté par Western Digital.

La technologie flash moderne domine le marché de plus de 50 milliards de dollars des dispositifs NVM en 2019 et constitue le segment le plus important de l'industrie mondiale des semi-conducteurs. Samsung est devenu le plus grand fournisseur de puces flash avec environ 30% du marché. Les autres principaux fournisseurs sont Toshiba et Western Digital.

Prix d'excellence du Sommet de la mémoire flash

Chaque année, le Sommet de la mémoire flash honore les personnes qui ont fait preuve de leadership dans l'avancement du développement, de l'utilisation de la mémoire flash et des technologies associées avec le Lifetime Achievement Award (LAA) . Les nominés non mentionnés ci-dessus comprenaient Kinam Kim de Samsung, qui a reçu un prix pour ses progrès dans le développement 3D NAND, et Dov Moran et Aryeh Mergi de M-Systems pour les innovations, y compris la mémoire flash intégrée dans les téléphones mobiles, les systèmes de fichiers pour Flash et clé USB.

Liens

1. C. T. Sah, “A new semiconductor tetrode, the surface-potential controlled transistor,” Proceedings of the IRE, vol. 49, no.11, (Nov. 1961) pp 1625.

2. C. T. Sah, “Evolution of the MOS transistor — from conception to VLSI,” Proceedings of the IEEE, Vol. 76, №10 (October 1988) p. 1295.

3. Edgar A. Sack and David A. Laws, “Westinghouse: Microcircuit Pioneer from Molecular Electronics to ICs,” IEEE Annals of the History of Computing, Vol. 34 (Jan.-March 2012) pp. 74–82.

4. Wegener, H.A.R., Lincoln, A.J., Pao, H.C., O’Connell, M.R., Oleksiak, R.E. Lawrence, H. “The variable threshold transistor, a new electrically-alterable, non-destructive read-only storage device,” Electron Devices Meeting, 1967 International, Vol. 13 (1967) p. 70

5. H. A. R. Wegener, “Investigation of New Concepts of Adaptive Devices,” NASA-CR-86114, Report no. SRRC-CR-68–43, Sept. 1968.

6. Dov Frohman-Bentchkowsky, “Integrated MNOS memory organization” US Patent 3641512A

7. Neale, R. G., D. L. Nelson, Gordon E. Moore, “Nonvolatile and reprogrammable the read-mostly memory is here,” Electronics (September 28, 1970) pp. 56–60.

8. Tarui, Yasuo; Hayashi, Yutaka; Nagai, Kiyoko “Proposal of electrically reprogrammable non-volatile semiconductor memory”. Proceedings of the 3rd Conference on Solid State Devices, Tokyo. The Japan Society of Applied Physics (1971–09–01): 155–162.

9. “MOS EPROM Forecast,” Dataquest SIS Prod., Mkt., & Tech. Report 0004718 (August 1989) p. 2

2. C. T. Sah, “Evolution of the MOS transistor — from conception to VLSI,” Proceedings of the IEEE, Vol. 76, №10 (October 1988) p. 1295.

3. Edgar A. Sack and David A. Laws, “Westinghouse: Microcircuit Pioneer from Molecular Electronics to ICs,” IEEE Annals of the History of Computing, Vol. 34 (Jan.-March 2012) pp. 74–82.

4. Wegener, H.A.R., Lincoln, A.J., Pao, H.C., O’Connell, M.R., Oleksiak, R.E. Lawrence, H. “The variable threshold transistor, a new electrically-alterable, non-destructive read-only storage device,” Electron Devices Meeting, 1967 International, Vol. 13 (1967) p. 70

5. H. A. R. Wegener, “Investigation of New Concepts of Adaptive Devices,” NASA-CR-86114, Report no. SRRC-CR-68–43, Sept. 1968.

6. Dov Frohman-Bentchkowsky, “Integrated MNOS memory organization” US Patent 3641512A

7. Neale, R. G., D. L. Nelson, Gordon E. Moore, “Nonvolatile and reprogrammable the read-mostly memory is here,” Electronics (September 28, 1970) pp. 56–60.

8. Tarui, Yasuo; Hayashi, Yutaka; Nagai, Kiyoko “Proposal of electrically reprogrammable non-volatile semiconductor memory”. Proceedings of the 3rd Conference on Solid State Devices, Tokyo. The Japan Society of Applied Physics (1971–09–01): 155–162.

9. “MOS EPROM Forecast,” Dataquest SIS Prod., Mkt., & Tech. Report 0004718 (August 1989) p. 2

Liens vers les transcriptions d'entrevue

, №0341, Science History Institute

, 102702214, Computer History Museum Collection

, 102745933, Computer History Museum Collection

Flash Intel, 102658199 Computer History Museum Collection

, 102740455, Computer History Museum Collection

, 102746703 Computer History Museum Collection

, 102746703 Computer History Museum Collection

, 500001027 Computer History Museum Collection

Entretien avec Charles C., catalogue 102746598 Collection du Computer History Museum

Entretien avec Simon Zee, catalogue 102746858 Computer History Museum Collection

La publicité

Nos serveurs épiques n'utilisent que des NAS NVMe triple réplication. Vous pouvez utiliser le serveur pour n'importe quelle tâche - développement, hébergement de sites, utilisation sous VPN et même obtention d'une machine distante sous Windows! Il peut y avoir beaucoup d'idées et nous vous aiderons à les traduire en réalité!