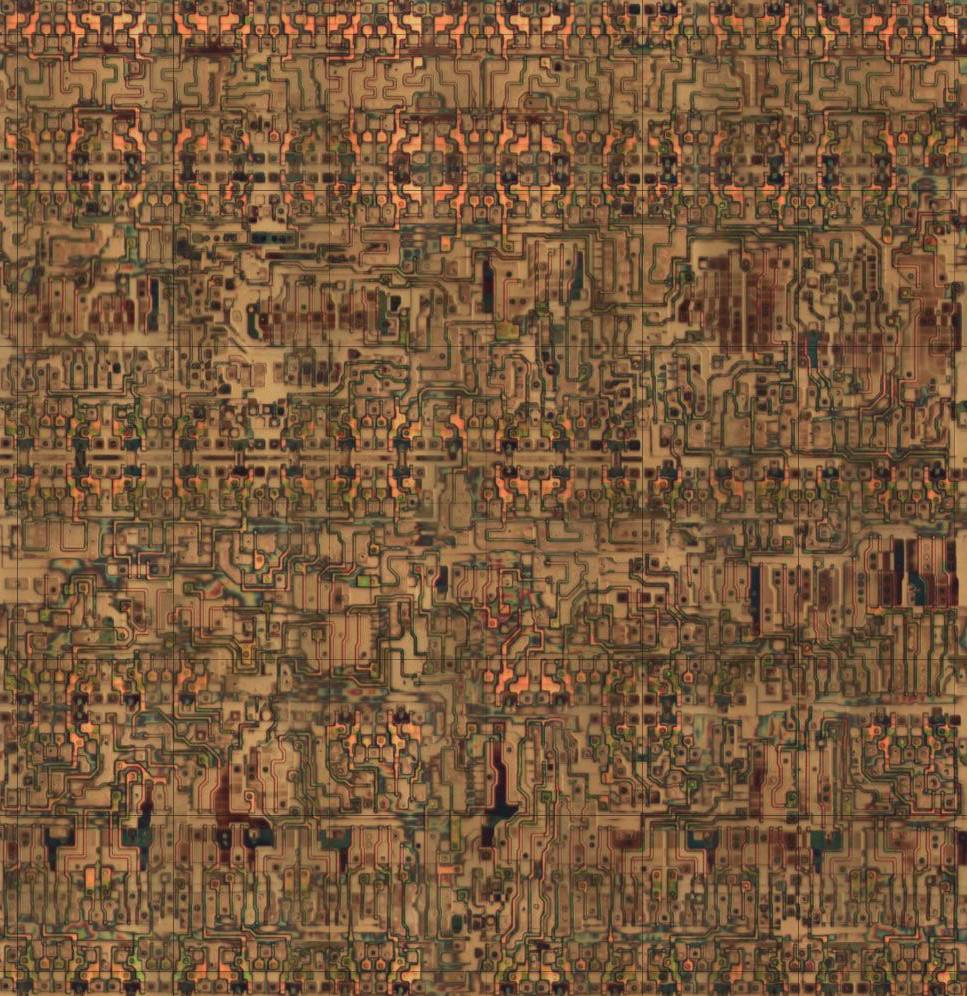

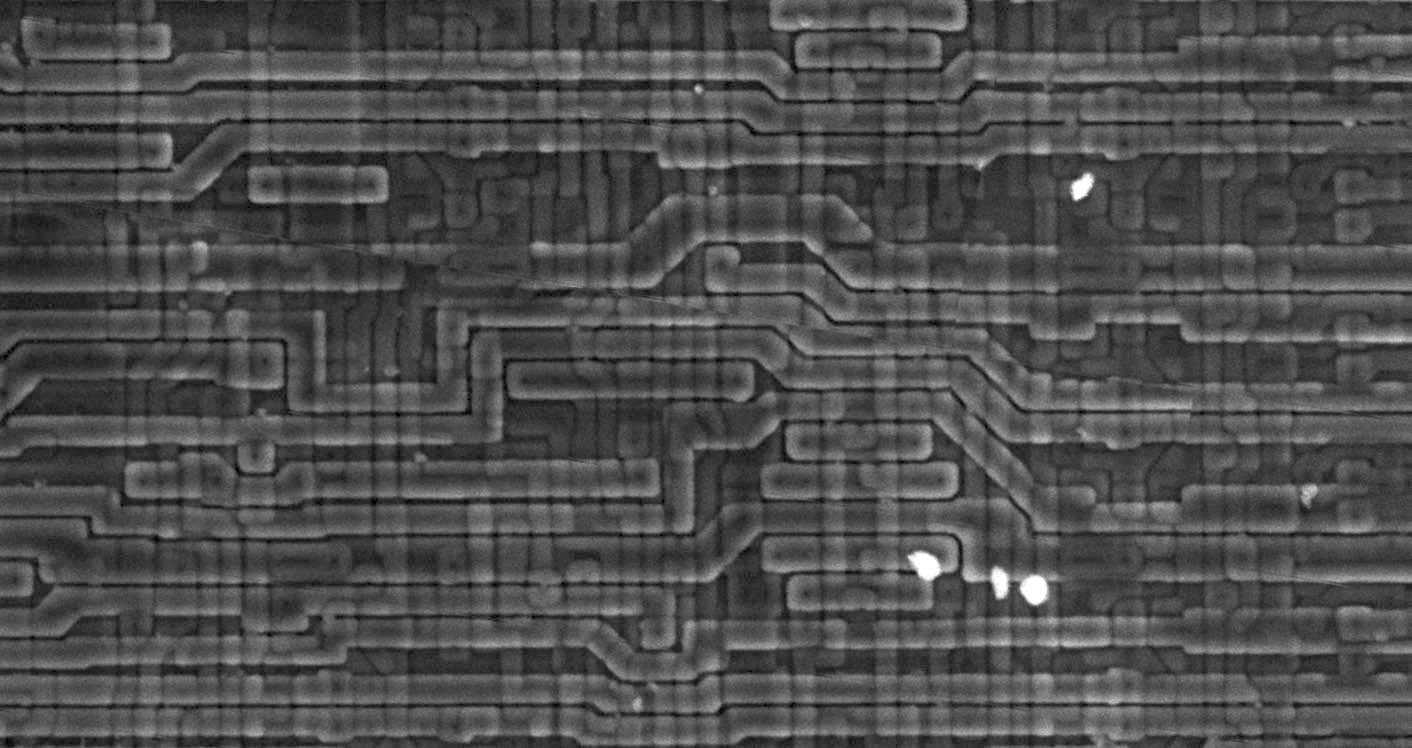

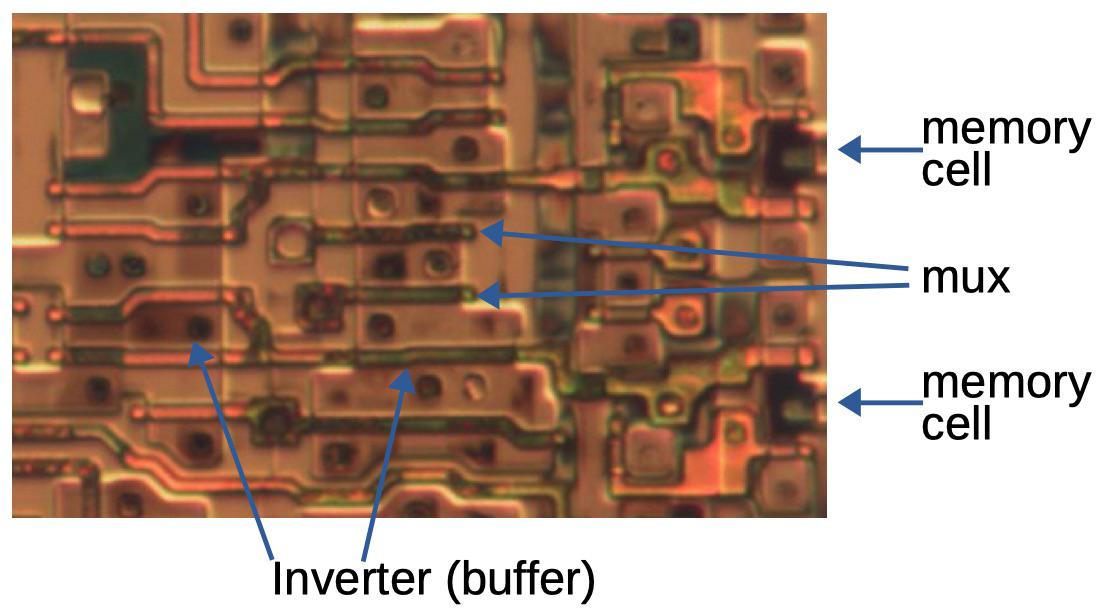

La photo montre l'un des 64 blocs de la puce XC2064. Les couches de métallisation sont supprimées, on peut voir des transistors en silicium et en polysilicium se trouvant sous la métallisation. Vous pouvez voir une photo à plus grande échelle ici: siliconpr0n .

Le FPGA a été inventé par Ross Freeman, co-fondateur de Xilinx en 1984, le premier FPGA était le XC2064. Il était beaucoup plus simple que les FPGA modernes, ne contenait que 64 blocs logiques, contre des milliers et des millions de FPGA modernes, et sa création a conduit à l'émergence d'une industrie valant des milliards de dollars. Le XC2064 est si important qu'il est entré dans le Chip Hall of Fame. J'ai procédé à une ingénierie inverse du XC2064 et dans cet article, j'explique sa structure interne en termes généraux et comment il est programmé avec un bitstream.

Xilinx

Xilinx -. , , Xilinx , . Xilinx Seiko Epson Semiconductor Division ( Seiko Epson).

XC2064

: ( ) . — (Programmable Logic Devices, PLD), , , 1967 . , , , . , PROM, , , EPROM, . , , Programmable Logic Array, Programmable Array Logic (1978), Generic Array Logic Uncommitted Logic Array. , , « », . , , , , , . , . "Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology." "A Brief History of FPGAs".

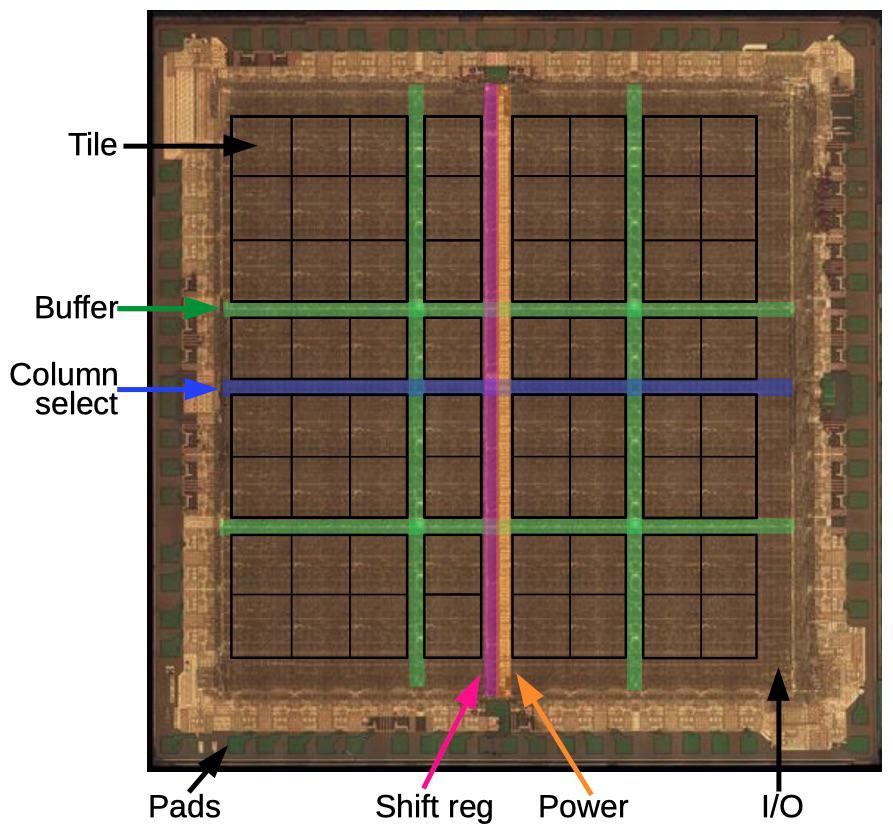

Xilinx XC2064 est la première puce FPGA. Tiré d'ici: siliconpr0n .

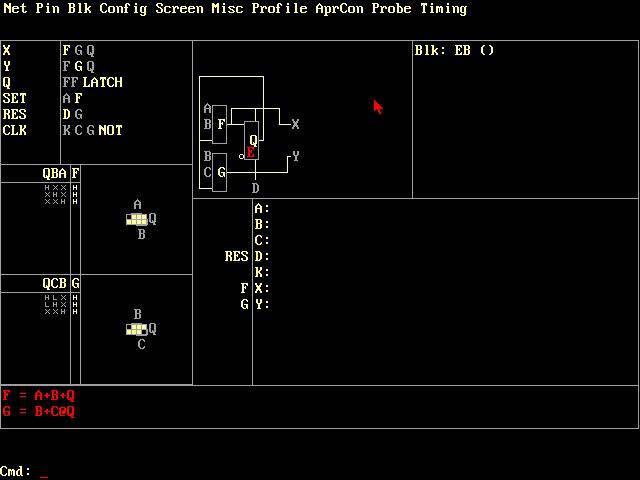

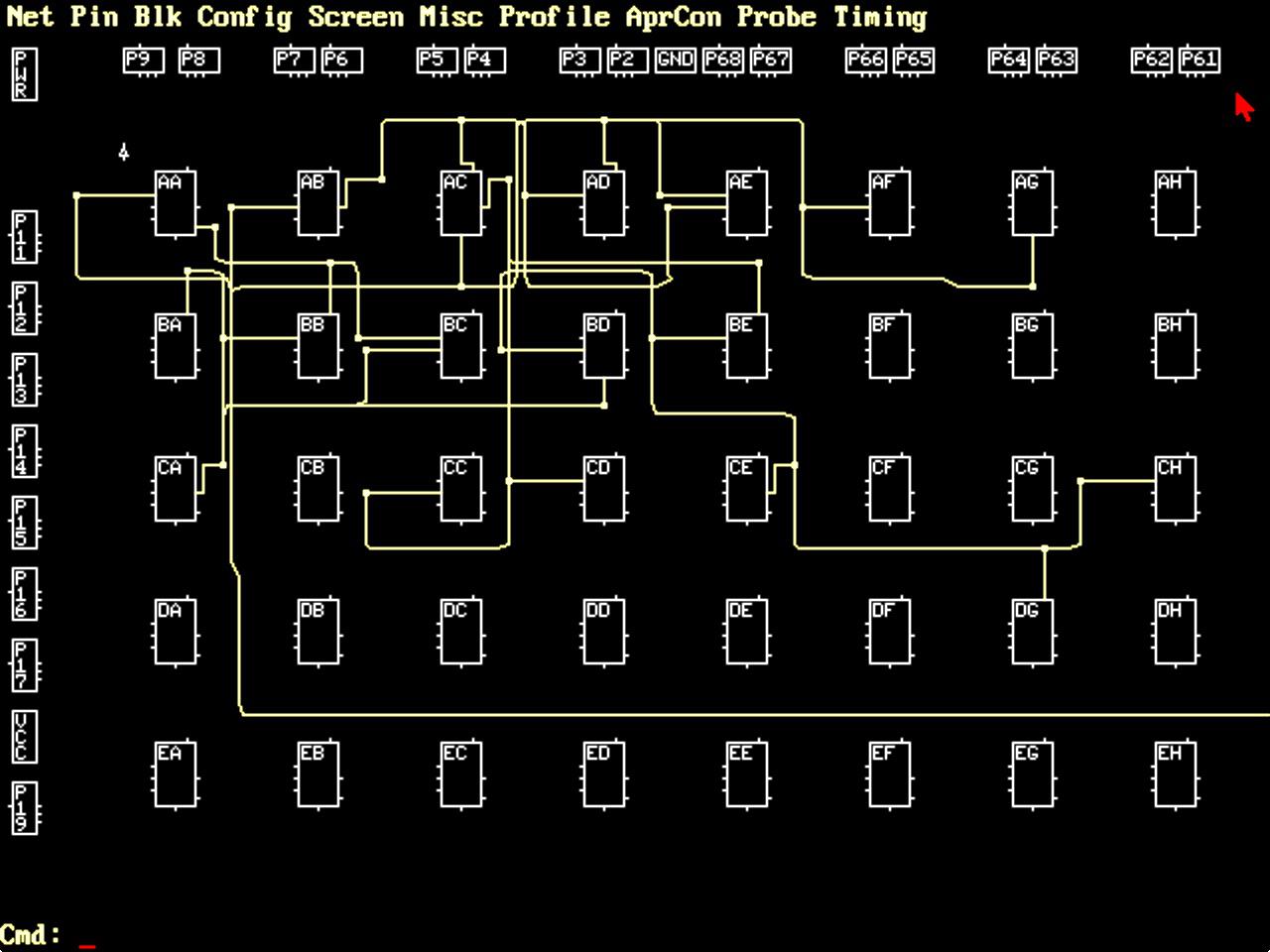

Les FPGA sont actuellement programmés dans des langages de description de matériel tels que Verilog ou VHDL, mais à l'époque, Xilinx fournissait son propre logiciel de développement, une application MS-DOS appelée XACT, pour la somme de 12 000 $. XACT fonctionnait à un niveau inférieur aux outils modernes: l'utilisateur définissait la fonction de chaque bloc logique, comme indiqué dans la capture d'écran ci-dessous, et les connexions entre les blocs logiques.

XACT a acheminé les connexions et généré un fichier de configuration (bitstream) qui a été chargé dans le FPGA.

Capture d'écran de XACT. Les deux tableaux F et G implémentent les équations affichées en bas de l'écran, avec la carte de Karnaugh ci-dessus.

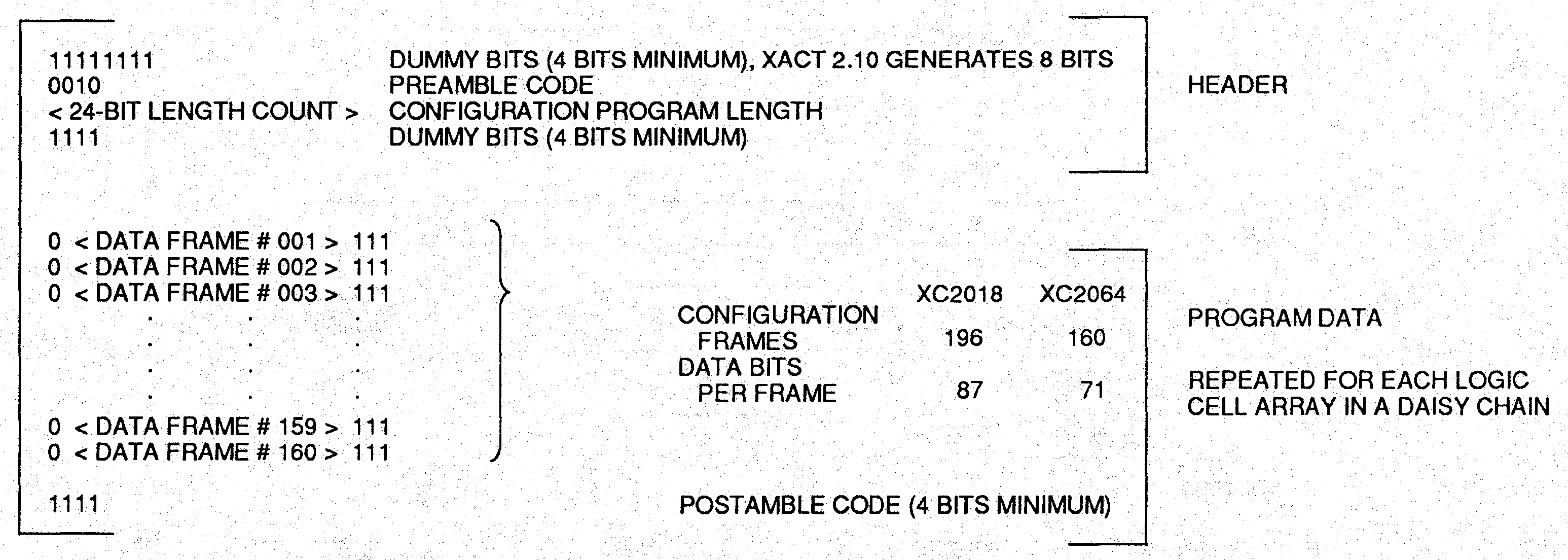

Le FPGA a été configuré en utilisant un train de bits, une séquence de bits dans un format propriétaire. Si vous regardez le flux binaire XC2064 (ci-dessous), vous verrez un mélange mystérieux de motifs qui se répètent de manière irrégulière et sont dispersés dans le flux binaire. Cependant, l'étude des circuits physiques du FPGA révèle la structure des données du train de bits et peut être étudiée.

Partie du train de bits généré par XACT.

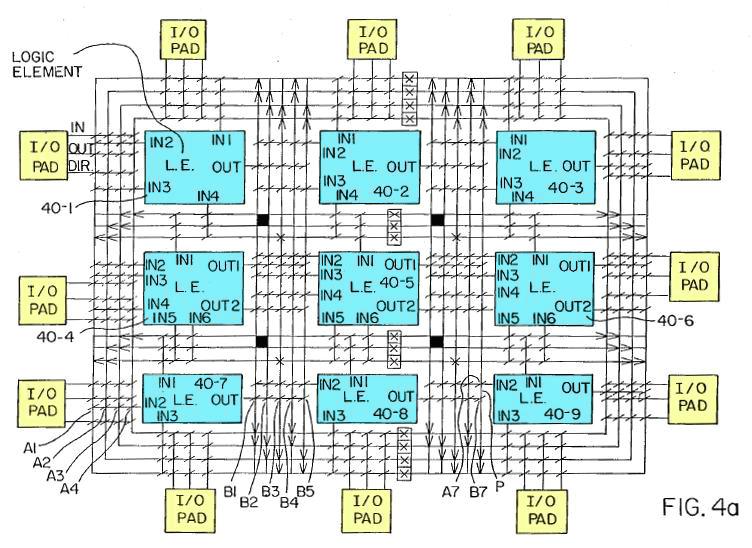

Comment fonctionne FPGA?

La figure ci-dessous, tirée du brevet FPGA original, montre la structure de base d'un FPGA. Ce FPGA simplifié a un total de 9 blocs logiques (marqués en bleu) et 12 ports d'E / S. Un réseau d'interconnexion relie les composants entre eux. En réglant des commutateurs (lignes diagonales) sur les connexions, les blocs logiques peuvent être connectés les uns aux autres et aux ports d'E / S. Chaque élément logique peut être programmé pour la fonction logique requise. En conséquence, une telle puce programmable peut implémenter n'importe quel appareil qui s'intègre dans l'espace disponible.

Brevet FPGA , blocs logiques (LE) interconnectés.

Bloc logique configurable (CLB)

Bien que l'image ci-dessus montre 9 CLB, le XC2064 a 64 CLB. La figure ci-dessous montre la structure du CLB. CLB a 4 entrées (A, B, C, D) et deux sorties (X et Y). Entre les deux se trouve la logique combinatoire, qui peut être programmée pour n'importe quelle fonction logique souhaitée. Le CLB contient également un déclencheur, dont la présence vous permet d'implémenter des compteurs, des registres à décalage, des machines à états et d'autres circuits avec état. Les trapèzes indiquent des multiplexeurs qui peuvent être programmés pour transmettre un signal provenant de l'une des entrées. Les multiplexeurs vous permettent de configurer le CLB pour une tâche spécifique en sélectionnant des signaux spécifiques pour contrôler le déclenchement et les sorties.

Bloc logique configurable dans XC2064, extrait d'ici: fiche technique .

Vous vous demandez peut-être comment la logique combinatoire implémente des fonctions logiques arbitraires. Y a-t-il un choix entre un ensemble de ET, OU, XOR, et ainsi de suite? Non, il existe une astuce astucieuse appelée table de recherche (LUT), qui est en fait la table de vérité de la fonction. Par exemple, une fonction de trois variables est définie par un tableau de 8 lignes. La LUT contient 8 bits de mémoire. Nous pouvons implémenter n'importe quelle fonction logique à 3 entrées tout en conservant ces trois bits.

Afficher les tableaux

XC2064 — , . CLB . XC2064 , 4 . , .

XC2064 . .

XC2064 . .

Connexions

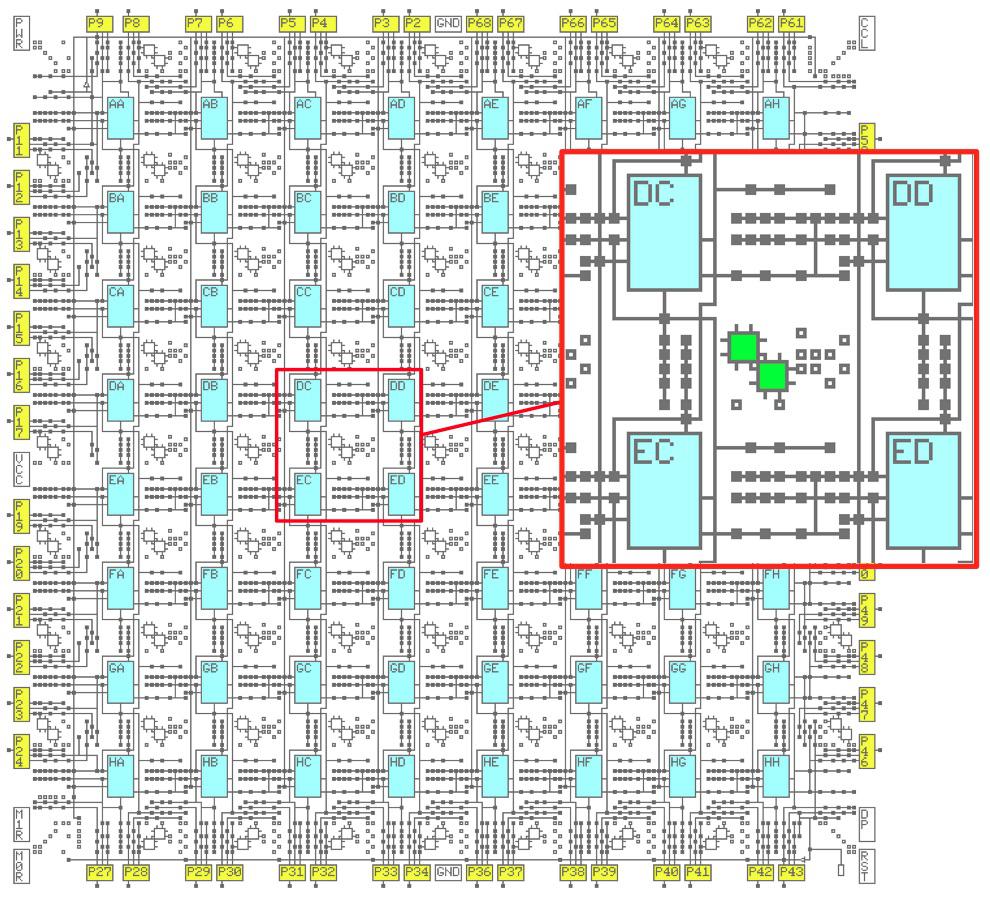

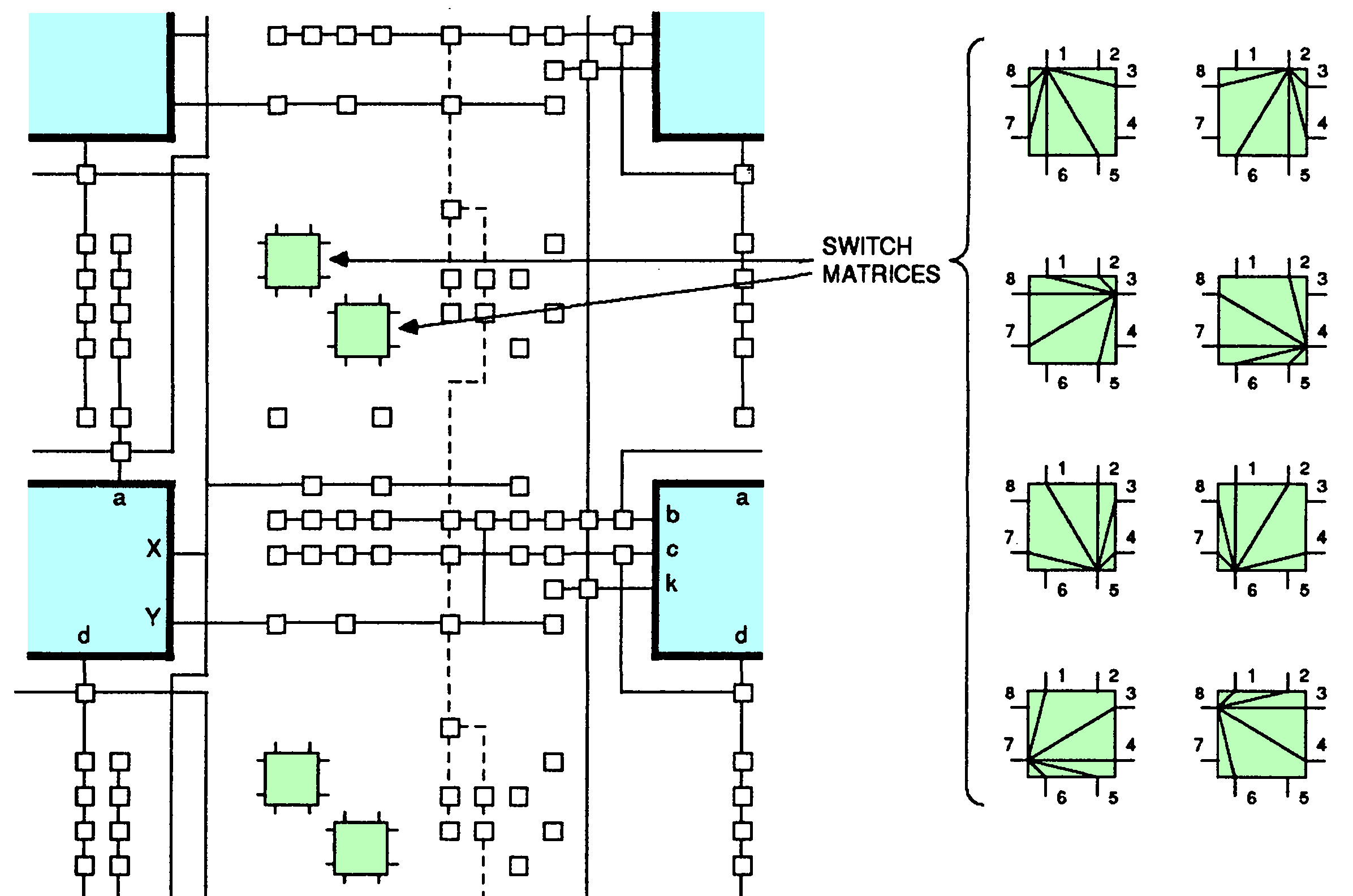

Le prochain aspect clé des FPGA est les connexions, qui peuvent être programmées pour commuter le CLB de différentes manières. Les connexions sont complexes, mais la description approximative est qu'il existe des segments de connexions verticales et horizontales entre tous les CLB. Vous pouvez connecter CLB avec des lignes horizontales et verticales et créer des connexions arbitraires. Un type de connexion plus complexe est la "matrice de commutation". Chaque matrice a 8 broches qui peuvent être connectées les unes aux autres (presque) de n'importe quelle manière.

La figure ci-dessous montre la structure des liaisons XC2064 qui fournissent des connexions entre les blocs logiques (bleu) et les lignes d'E / S (jaune). L'encart montre les détails du mécanisme d'accouplement. Les rectangles verts sont des matrices d'interrupteurs à 8 broches et les petits carrés sont les points de connexion programmables.

Le FPGA XC2064 possède une matrice CLB 8x8. Chaque CLB a un nom de AA à HH.

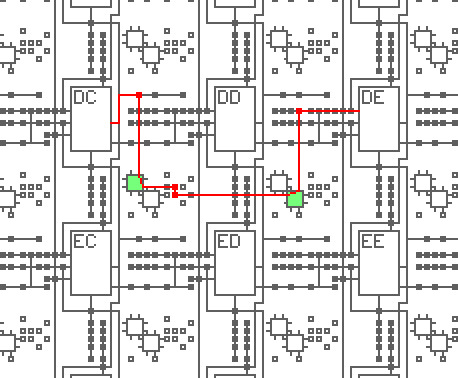

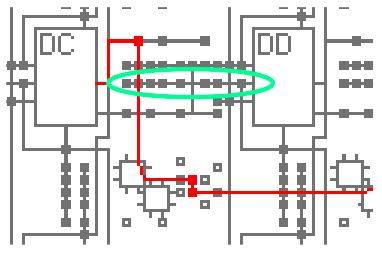

La connexion peut commuter, par exemple, la sortie d'un bloc DC vers une entrée d'un bloc DE, comme illustré ci-dessous. La ligne rouge montre le chemin du signal et les petits carrés rouges indiquent les points de connexion activés. Après avoir quitté le bloc DC, le signal est acheminé vers le premier point de connexion sur un commutateur à 8 broches (vert), qui l'achemine à travers deux points de connexion et un autre commutateur à 8 voies (lignes verticales et horizontales inutilisées non illustrées). Notez que la connexion est assez complexe, même un chemin aussi court utilise quatre points de connexion et deux commutateurs.

Exemple d'acheminement du signal de la sortie d'un bloc DC vers un bloc DE.

La capture d'écran ci-dessous montre comment le traçage est effectué dans XACT. Les lignes jaunes indiquent les connexions entre les blocs logiques. À mesure que le nombre de signaux augmente, il devient difficile d'établir des connexions sans conflit entre les chemins. XACT trace automatiquement, mais la trace peut également être modifiée manuellement.

Capture d'écran du programme XACT. Il s'agit d'un programme MS-DOS contrôlé par le clavier et la souris.

la mise en oeuvre

Ensuite, nous examinerons les circuits internes du XC2064 par rétro-ingénierie à partir d'une photo du cristal. Soyez averti que cela nécessite une certaine familiarité avec le XC2064.

Photo en cristal

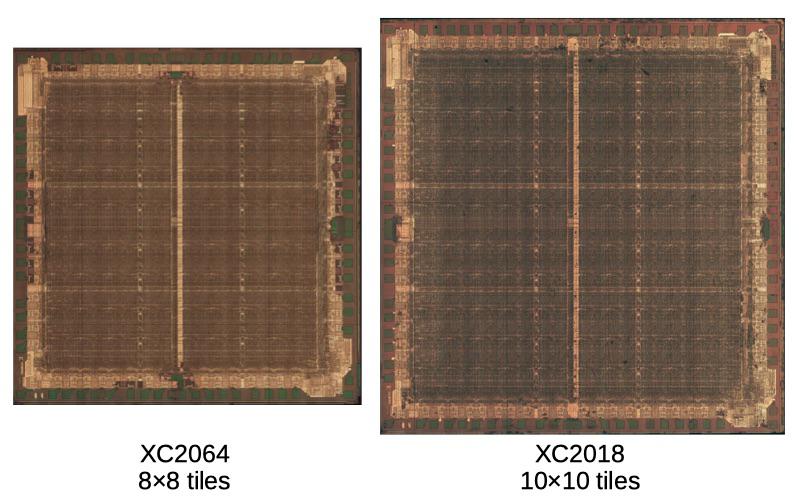

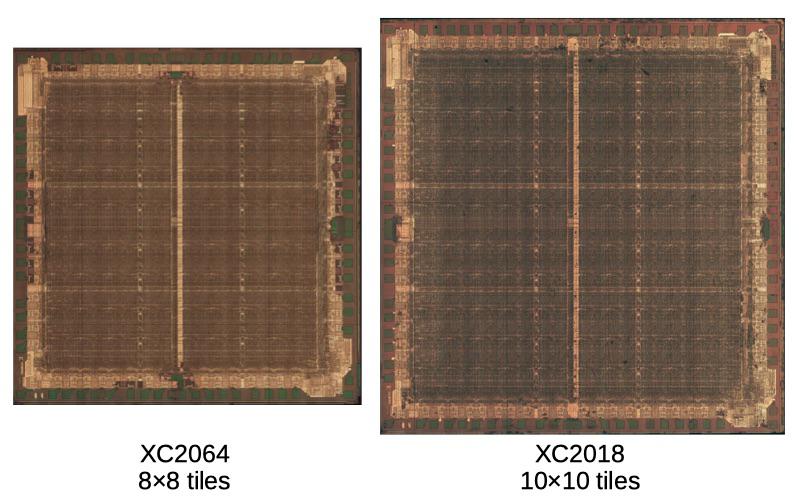

XC2064 XC20186, XC2064 XC2018 siliconpr0n. , . John McMaster , , . , .

XC2064 , John McMaster.

XC2064 , John McMaster.

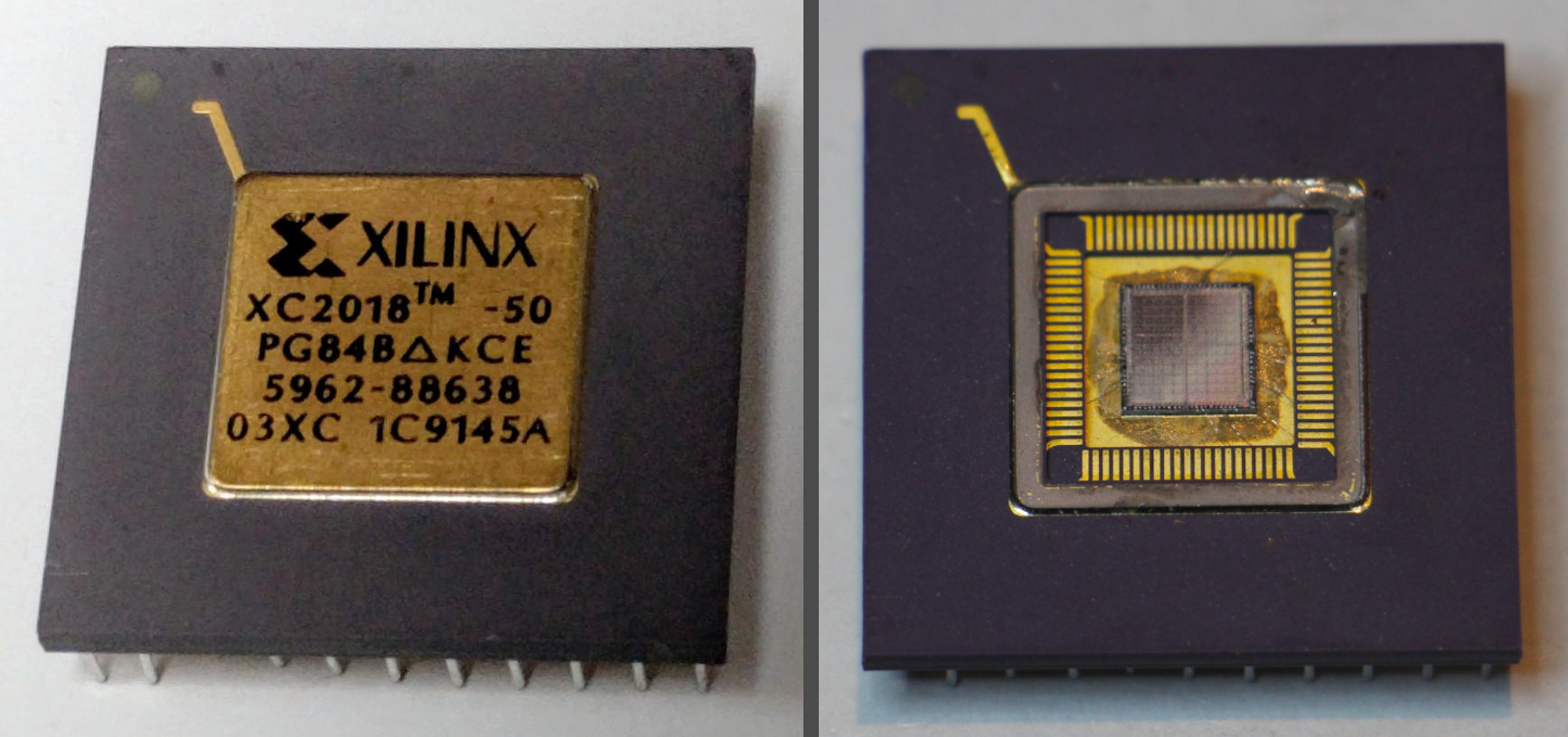

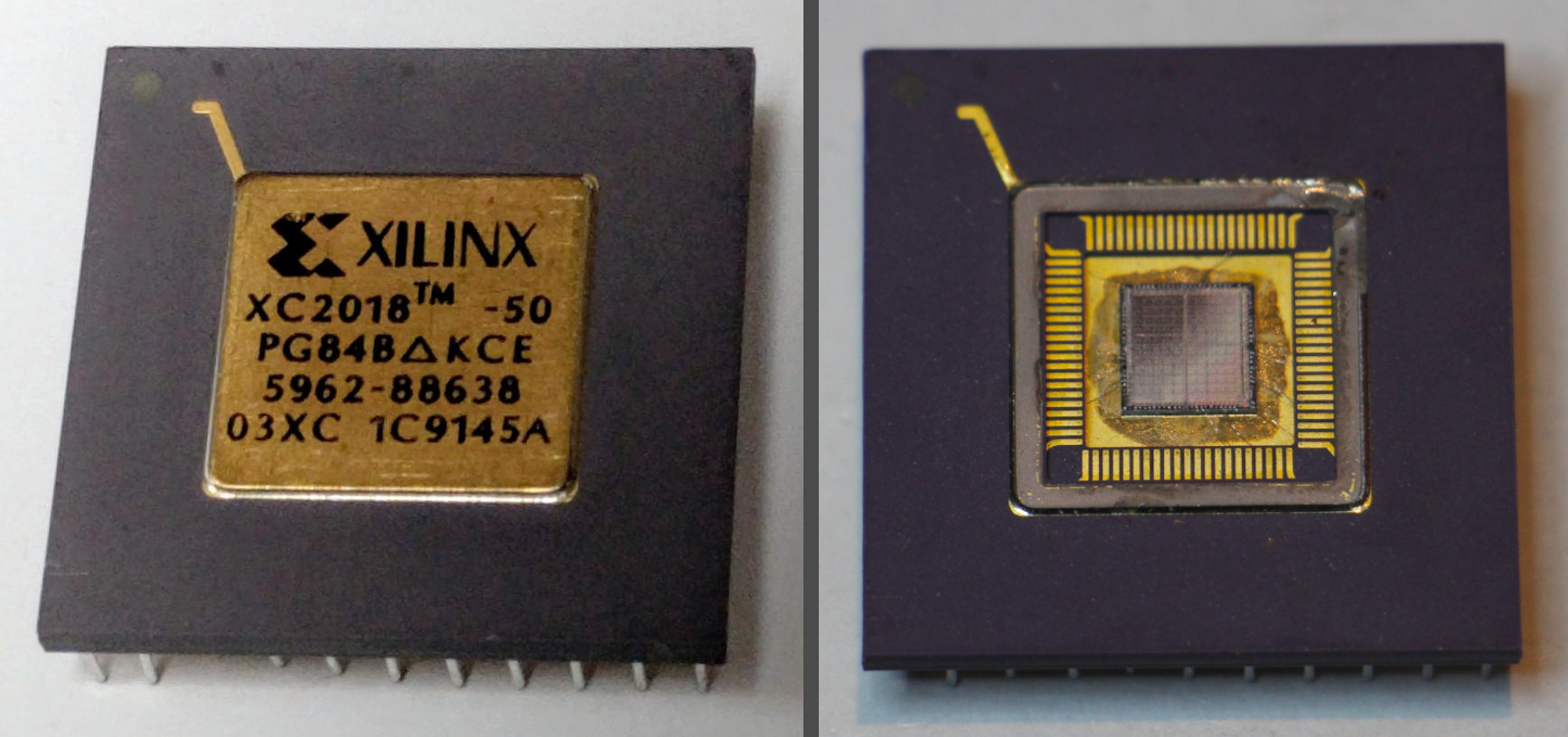

XC2018

Xilinx XC2018 ( ) 100 , , XC2064. , XC2064 64 , 1010, 88. XC2018 , .

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

Ci-dessous, une photo du cristal XC2064. La partie principale du FPGA est une matrice de 8x8 blocs, dont chacun contient un bloc logique et les circuits environnants. Bien que le diagramme FPGA montre les blocs logiques (CLB) comme séparés des schémas de câblage d'entité, en réalité ce n'est pas le cas. En fait, chaque bloc logique et son environnement sont implémentés comme un seul nœud, une tuile. (Pour être précis, la vignette comprend les connexions en haut et à gauche de chaque CLB.)

Disposition des blocs XC2064. Tiré d'ici: siliconpr0n .

Situés le long des côtés du circuit intégré, les blocs d'E / S assurent la communication avec le monde extérieur. Ils sont connectés aux broches du cristal, qui sont représentées par de petits carrés verts, et connectés aux broches du boîtier du microcircuit. Il y a des tampons sur le dé (vert): deux verticaux et deux horizontaux. Ces tampons amplifient le signal qui parcourt une longue distance à travers la puce et réduisent la latence. Le registre à décalage vertical (rose) et la chaîne de récupération de colonne horizontale sont utilisés pour charger le train de bits dans la puce, comme illustré ci-dessous.

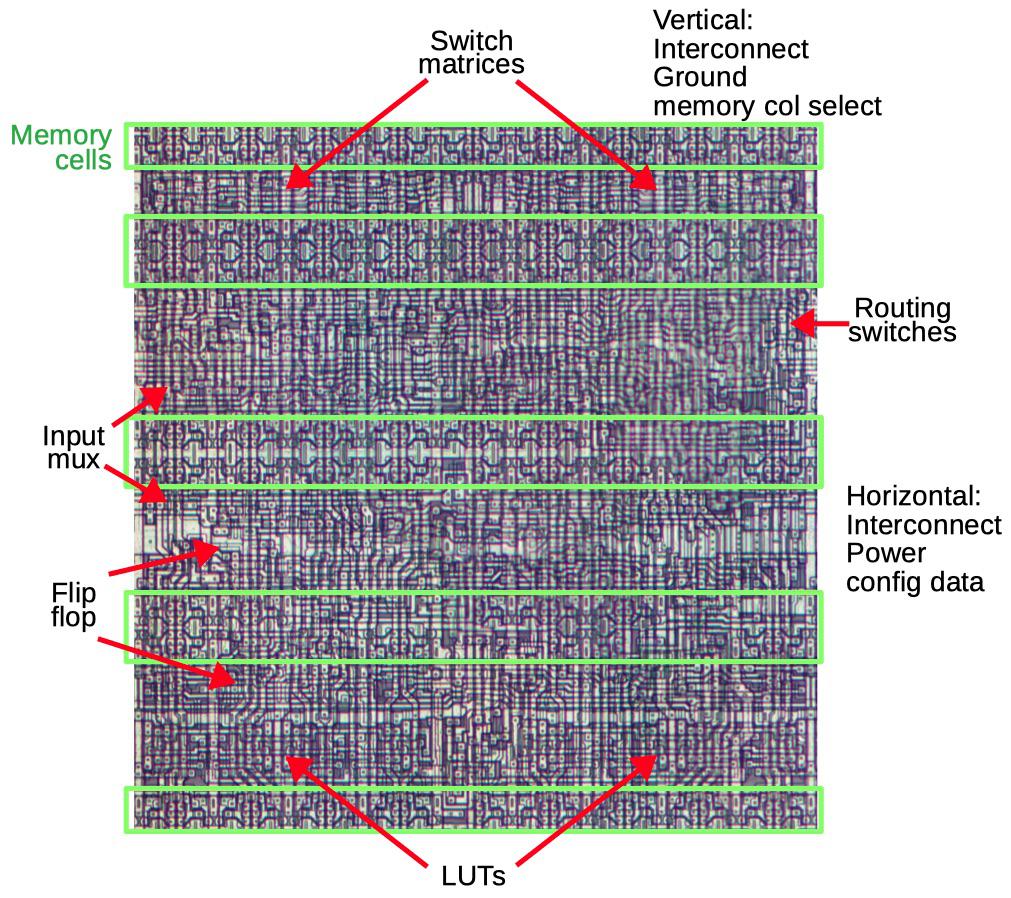

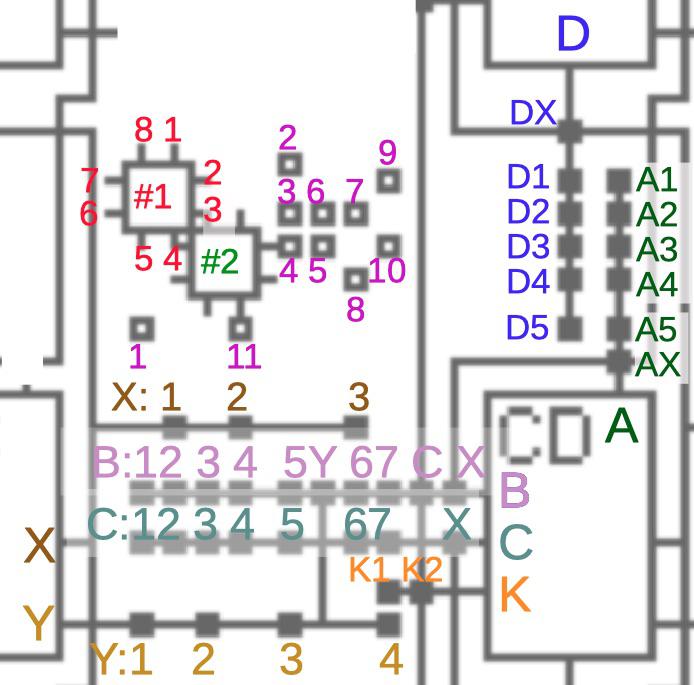

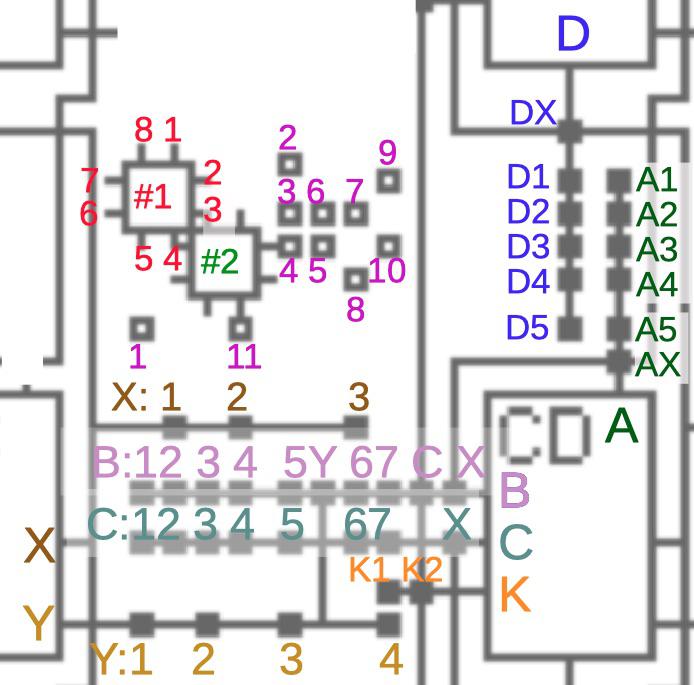

À l'intérieur des carreaux

La figure ci-dessous montre la structure d'une tuile XC2064, la puce contient 64 tuiles de ce type emballées sur un dé. Environ 40% de chaque tuile est occupée par des cellules de mémoire (affichées en vert) qui stockent des bits de configuration. Le tiers supérieur (approximativement) de la tuile contient les schémas de connexion: deux matrices de commutation et un certain nombre de commutateurs de liaison individuels. Voici le bloc logique. La partie principale du bloc logique est le multiplexeur d'entrée, la bascule et la table de consultation. La tuile est connectée aux voisins par des lignes de communication horizontales et verticales, et elle est également connectée aux rails d'alimentation et de masse. Les bits de données de configuration entrent dans les cellules de mémoire horizontalement et les signaux verticaux sélectionnent une colonne spécifique à charger.

Une tuile FPGA montrant les nœuds fonctionnels importants

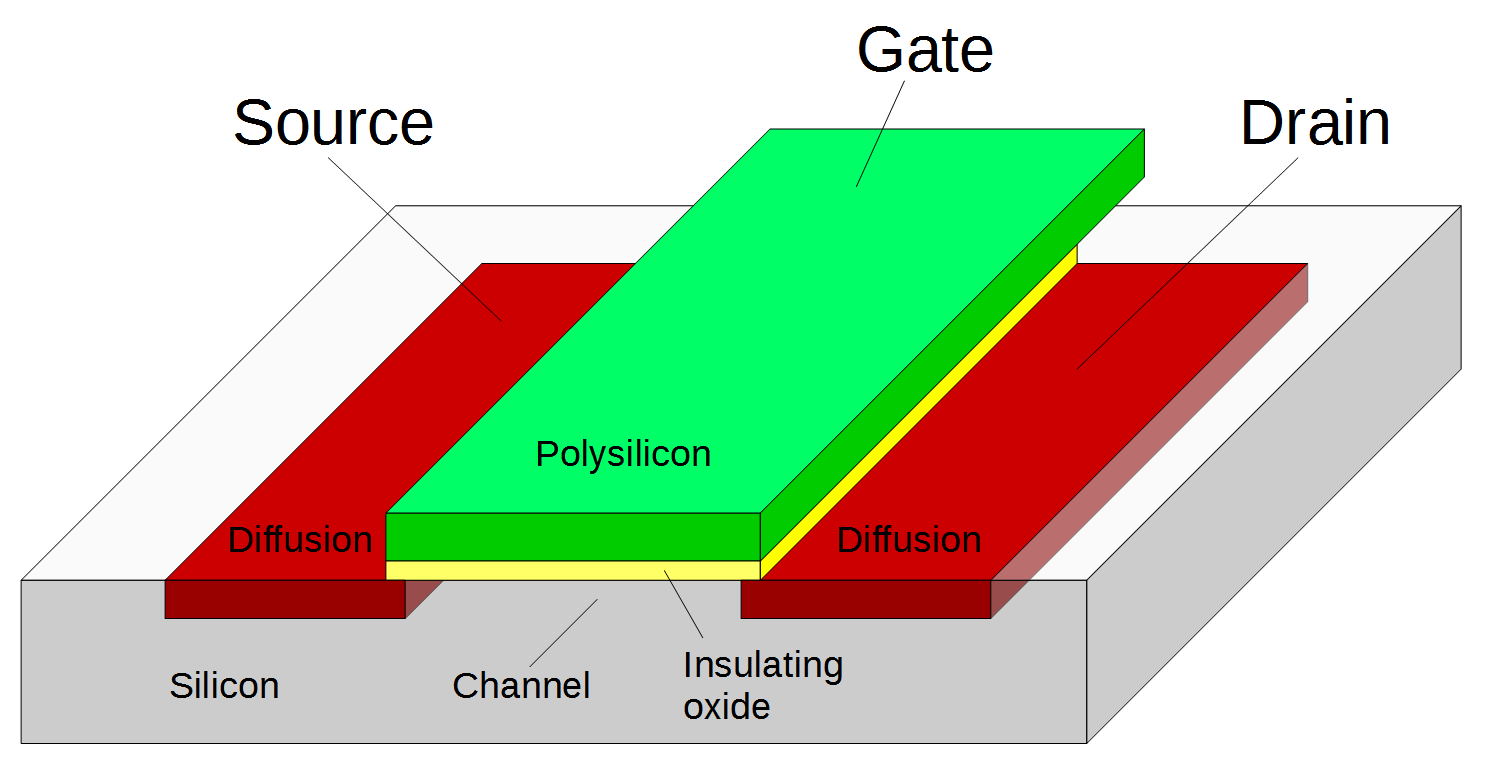

Transistors

FPGA est implémenté sur une logique CMOS (CMOS), construite à partir de transistors NMOS et PMOS. Les transistors jouent deux rôles principaux dans les FPGA. Premièrement, les éléments logiques sont formés à partir de leurs combinaisons. Deuxièmement, les transistors sont utilisés comme commutateurs par lesquels passe un signal, par exemple, pour former des connexions entre des blocs. Un transistor qui remplit ce rôle est appelé transistor traversant. La figure ci-dessous montre la structure de base d'un MOSFET. Deux sections de silicium sont dopées avec des impuretés pour créer un drain et une source. Entre eux se trouve une grille qui allume et éteint le transistor et contrôle le courant entre le drain et la source. L'obturateur est constitué d'un type spécial de silicium appelé polysilicium, isolé du silicium en dessous par une fine couche d'oxyde. Au-dessus, il y a deux couches de métallisation, qui fournissent des connexions de circuit.

Structure du MOSFET

Sur la photo du cristal, nous pouvons observer à quoi ressemble le transistor au microscope. La grille en polysilicium est une ligne serpentine entre deux régions dopées de silicium. Les cercles sont des vias reliant le silicium et la couche métallique (qui est supprimée sur cette photo).

MOSFET FPGA

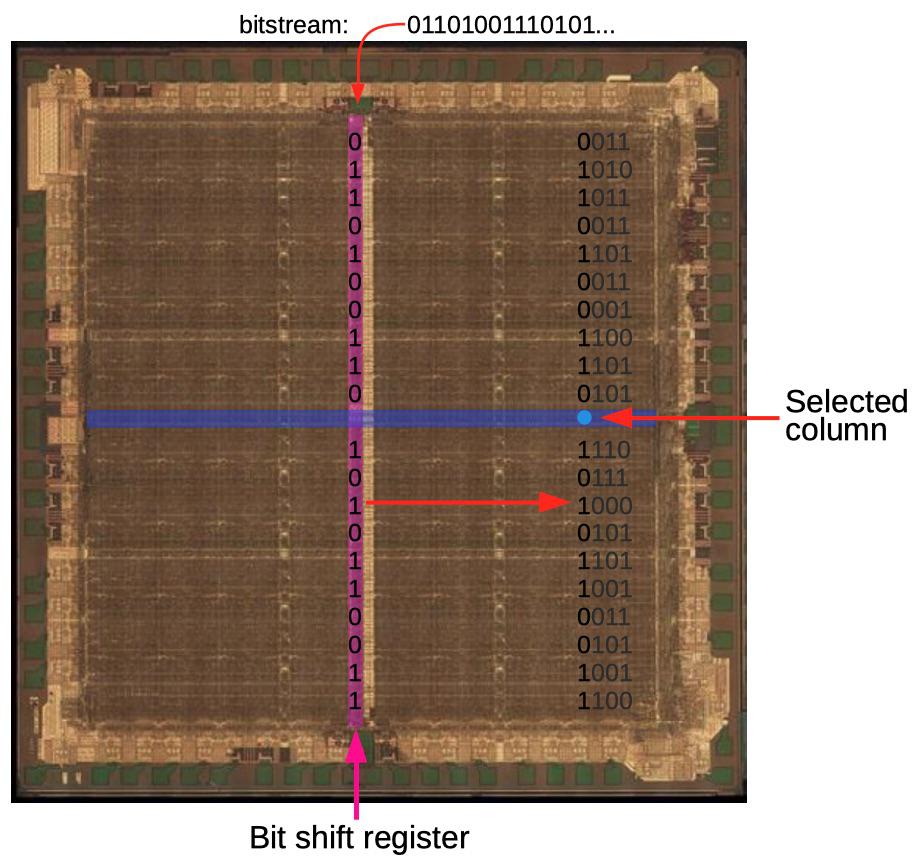

Bitstream et mémoire de configuration

Les informations de configuration du XC2064 sont stockées dans les emplacements de mémoire de configuration. Le FPGA n'utilise pas de mémoire bloc pour cela, à la place, la mémoire de configuration est répartie dans tout le cristal sous la forme d'une grille 160x71, chaque bit est placé à côté du circuit qu'il contrôle. La figure ci-dessous montre le train de bits de configuration chargé dans le FPGA. Le train de bits est chargé dans le registre à décalage qui va au milieu de la puce (rose). Une fois que 71 bits sont chargés dans le registre à décalage, le circuit d'extraction de colonne (bleu) sélectionne la colonne de mémoire souhaitée et les bits sont chargés dans la colonne en parallèle. Ensuite, les 71 bits suivants sont chargés dans le registre à décalage et la colonne suivante à gauche est sélectionnée. Le processus est répété pour les 160 colonnes du FPGA et le train de bits entier est chargé dans le FPGA. L'utilisation d'un registre à décalage élimine le besoin de grands circuits d'adressage de mémoire.

Comment le train de bits est chargé dans le FPGA. Les bits sont représentés de manière conventionnelle, le stockage réel des bits est beaucoup plus dense. Les trois colonnes de droite ont déjà été chargées et la quatrième est en cours de chargement. La photo du cristal est prise d'ici: siliconpr0n .

L'important est que le train de bits soit distribué à travers la puce dans exactement l'ordre dans lequel les bits apparaissent dans le fichier: le conditionnement des bits dans le train de bits correspond à leur placement physique sur la puce. Comme indiqué ci-dessous, chaque bit est stocké dans le FPGA à côté du circuit qu'il contrôle. ainsi, le format de fichier de train binaire est directement déterminé par le placement des circuits matériels. Par exemple, s'il y a un espace entre les tuiles et qu'il y a un tampon dedans, le même intervalle sera dans le train de bits. La structure du train de bits ne dépend pas d'abstractions logicielles telles que les champs dans les tables de données ou les blocs de configuration. Comprendre le bitstream nécessite une réflexion en termes de matériel, pas de logiciel

Bitstream

, (.RBT) , .

, .

, .

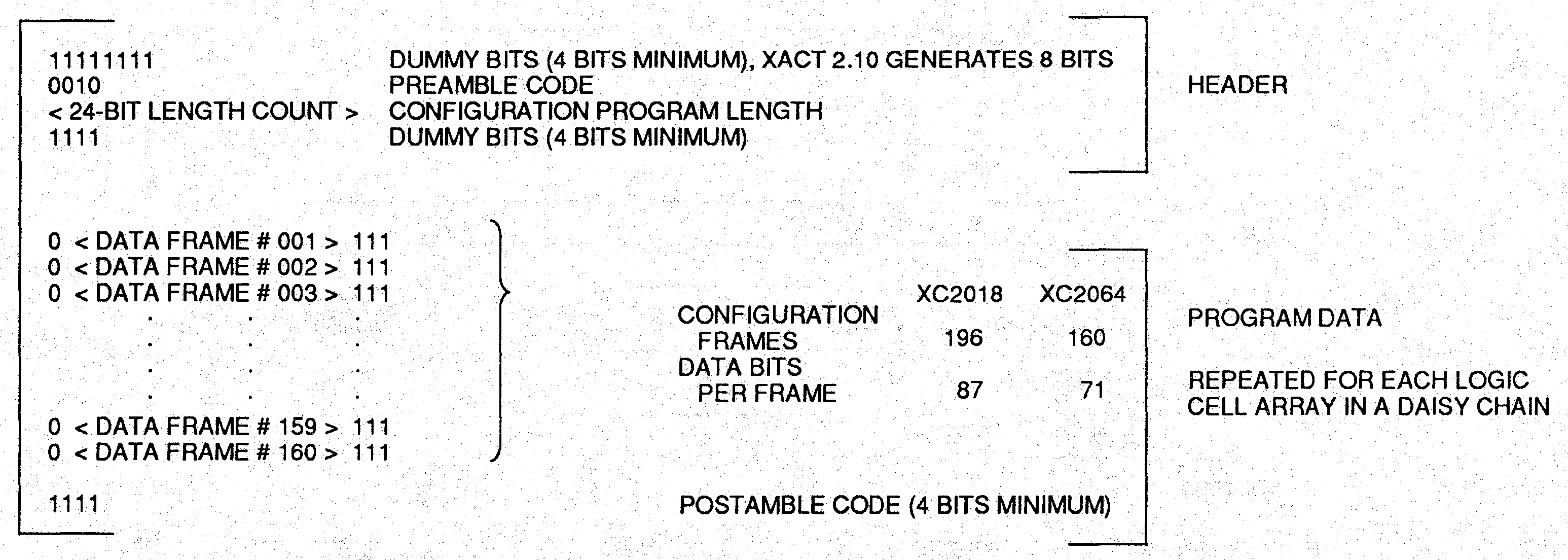

Chaque bit de mémoire de configuration est implémenté comme indiqué ci-dessous. Chaque cellule mémoire est constituée de deux onduleurs connectés en boucle. un tel circuit a deux états stables, et peut stocker un bit: soit l'onduleur supérieur est à l'état 1, et l'onduleur inférieur est à l'état 0, soit vice versa. Pour écrire dans la cellule, le transistor de passage à gauche est activé, faisant passer le signal. Le signal sur la ligne de données tire simplement l'onduleur en écrivant le bit requis. (Vous pouvez également lire les données de configuration en utilisant le même échelon.) La sortie Q et le Q inversé contrôlent une fonction spécifique dans le FPGA, comme la fermeture d'un réseau d'interconnexion, la récupération d'un bit dans une table de consultation ou le contrôle d'un déclencheur. Dans la plupart des cas, seule la sortie Q est utilisée.

Cellule SRAM

(SRAM). , RAM, , , SRAM. , 5T SRAM.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

Schéma d'un bit de mémoire de configuration, issu de la documentation.

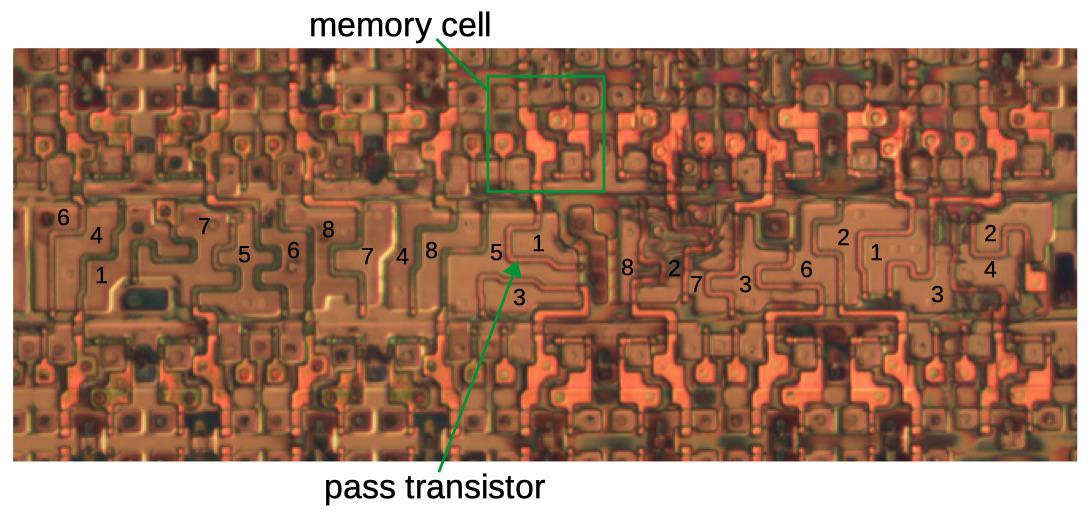

La figure ci-dessous montre la structure physique des cellules de mémoire. La photo de gauche montre 8 cellules mémoire, dont l'une est mise en évidence. Chaque ligne de données horizontale est connectée à tous les emplacements de mémoire de la ligne. Chaque ligne de récupération de colonne sélectionne tous les emplacements de mémoire dans la colonne, permettant l'écriture. La photo du milieu montre des sections de silicium et de polysilicium pour une cellule mémoire. Les couches de métal ont été retirées pour exposer les transistors en dessous. Les couches de métallisation relient des transistors, des cercles sur la photo, ce sont des connexions, des vias, entre le silicium ou le polysilicium et le métal. Le diagramme montre comment cinq transistors sont connectés, le placement des éléments sur le diagramme correspond à leur placement sur la photo. Deux paires de transistors forment les inverseurs CMOS, avec un transistor traversant en bas à gauche donnant accès à la cellule.

, . — . , . . : siliconpr0n.

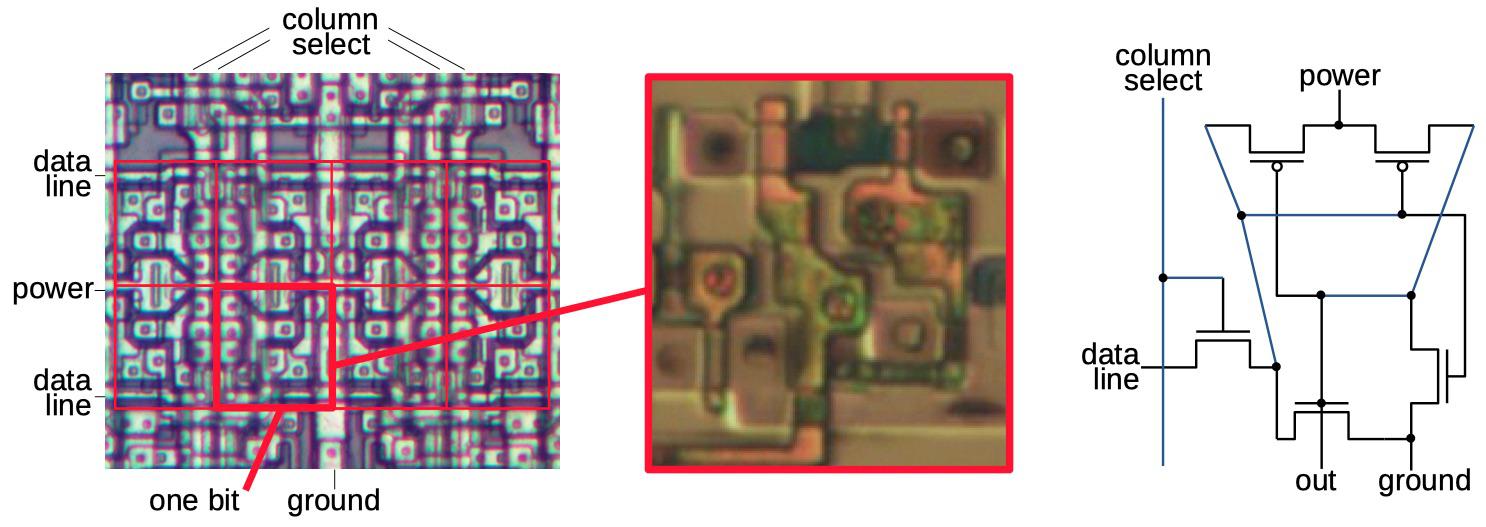

Comme expliqué précédemment, FPGA implémente des fonctions logiques arbitraires à l'aide de tables de consultation. La figure ci-dessous montre comment la table de consultation est implémentée dans XC2064. Les huit valeurs de gauche sont stockées dans huit emplacements de mémoire. Quatre multiplexeurs sélectionnent une de chaque paire de valeurs, en fonction de la valeur à l'entrée A, si A = 0, la valeur supérieure des valeurs est sélectionnée, si A = 1, puis la valeur inférieure. Ensuite, le grand multiplexeur choisit l'une des quatre valeurs en fonction des signaux B et C. Le résultat sera une valeur spécifique, dans ce cas A XOR B XOR C. Nous pouvons faire n'importe quelle fonction logique si nous substituons différentes valeurs dans le tableau.

Implémentation XOR dans la table de recherche.

Chaque multiplexeur est implémenté à l'aide de transistors pass-through. En fonction des signaux de commande, l'un des transistors pass-through est activé, transmettant les données de l'entrée à la sortie. La figure ci-dessous montre une partie de la chaîne LUT, avec deux bits multiplexés. Sur la droite se trouvent deux emplacements de mémoire. Chaque bit est passé à travers l'inverseur, amplifié et passé à travers les transistors pass-through du multiplexeur au milieu, sélectionnant l'un de ces bits.

Vue des filets qui implémentent la LUT. Tiré de siliconpr0n.

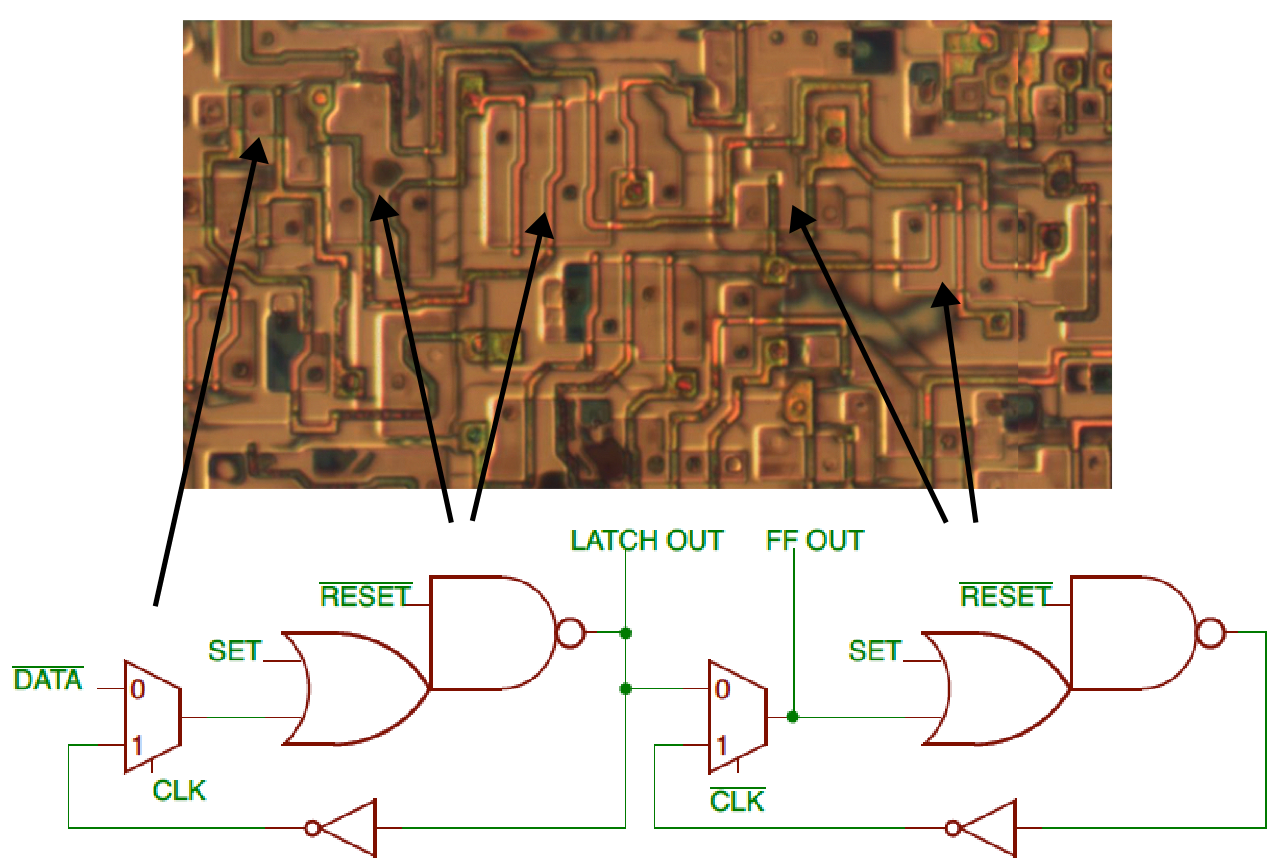

Déclencheur

Chaque CLB contient une bascule qui permet au FPGA d'implémenter des verrous, des machines d'état et d'autres réseaux avec état. La figure ci-dessous montre une implémentation de déclencheur (quelque peu inhabituelle). Elle utilise le schéma suivant. Lorsque le signal d'horloge est égal à zéro, le premier multiplexeur transmet les données au premier verrou, qui stocke la valeur. Le bit est inversé deux fois, lorsqu'il passe par les portes OU, NAND et inverseur, et reste le même en conséquence. en outre, le deuxième multiplexeur à verrouillage reçoit le bit du premier verrouillage lorsque l'horloge monte à 1 (notez que l'horloge est inversée). Cette valeur est la sortie de la bascule. Lorsque le signal d'horloge est mis à 0, le multiplexeur secondaire ferme la boucle en verrouillant le bit. Ainsi, le déclencheur est sensible au front du signal,verrouiller la valeur sur le front avant du signal d'horloge. Définissez et réinitialisez les lignes et réinitialisez la bascule.

. OR-NAND : siliconpr0n.

La matrice de commutation est un élément d'interconnexion important. Chaque commutateur a 8 broches (deux de chaque côté) et peut les connecter de presque toutes les manières. Les signaux peuvent être déroulés, divisés, intersectés avec plus de flexibilité qu'au niveau des nœuds d'interconnexion individuels. La figure ci-dessous montre une partie du réseau d'interconnexion entre les quatre CLB (bleu). Les matrices de commutation (vertes) peuvent être connectées dans n'importe quelle combinaison de connexions sur le côté droit. Notez que chaque broche peut être connectée à d'autres broches à raison de 5 à 7 pièces. Par exemple, la broche 1 peut être connectée à la broche 3, mais pas aux broches 2 et 4. Cela rend la matrice presque complète, avec 20 connexions possibles au lieu de 28.

À partir de là: Xilinx Programmable Gate Array Data Book , fig. 7b.

La matrice de commutation est formée de rangées de transistors commandés par les cellules mémoire au-dessus et en dessous d'elles. Les deux côtés du transistor sont deux broches de la matrice de commutation qui peuvent être connectées par le transistor. Ainsi, chaque matrice a 20 bits de contrôle, deux matrices par tuile nous donnent 40 bits par tuile. La photo ci-dessous montre une cellule mémoire connectée à la grille ondulée du transistor passe en dessous. Ce transistor assure la connexion entre la broche 5 et la broche 1. Ainsi, le bit du train binaire correspondant à cet emplacement mémoire commande la connexion entre les broches 5 et 1. De même, d'autres cellules mémoire et leurs transistors associés commandent d'autres connexions. Notez également que l'ordre de ces connexions ne suit aucun modèle particulier, par conséquent,la correspondance entre les bits du train de bits et les broches de commutation semble aléatoire.

Matrice de commutation

20 . 18 , .

Implémentation d'une matrice de connexions 8 fils. Les régions de silicium sont désignées par les numéros de leurs broches correspondantes. Les couches métalliques reliant les conducteurs correspondants aux transistors ont été supprimées. Tiré de siliconpr0n.

Connexions d'entrée

Les entrées CLB utilisent un schéma de codage de train binaire différent, qui est expliqué par sa mise en œuvre matérielle. Dans l'image ci-dessous, les huit nœuds ellipsés sont des entrées potentielles vers le CLB appelé DD. Un seul nœud (maximum) peut être configuré comme entrée, car la connexion de deux signaux à une entrée peut les court-circuiter ensemble.

Sélection d'entrée. Les huit entrées entourées en vert sont des entrées DD potentielles, une seule d'entre elles peut être sélectionnée.

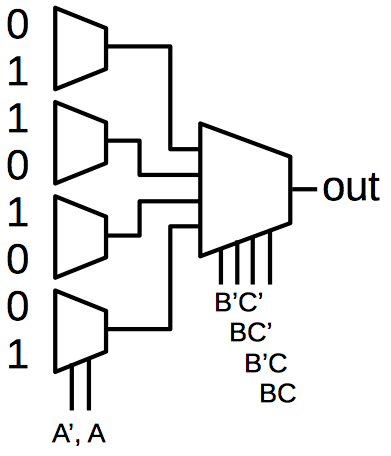

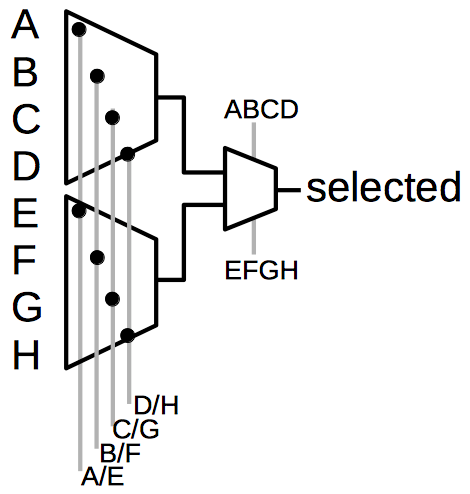

L'entrée requise est sélectionnée par le multiplexeur. Une solution simple serait d'utiliser un multiplexeur à 8 entrées avec trois bits de contrôle choisissant l'un des 8 signaux. Une autre solution simple consisterait à utiliser 8 transistors de passage, chacun avec son propre signal de commande, dont l'un sélectionne le signal requis. Cependant, le FPGA utilise une approche hybride qui élimine le besoin d'un décodeur dans le premier cas, mais nécessite 5 signaux de commande au lieu des 8 requis dans la seconde approche.

Le FPGA utilise des multiplexeurs pour sélectionner l'une des huit entrées.

Le diagramme de la figure ci-dessus montre le multiplexeur à deux couches utilisé dans le FPGA. Au premier étage, l'un des signaux de commande est activé. Dans la deuxième étape, le signal haut ou bas est sélectionné et appliqué à la sortie. Par exemple, supposons que le signal de commande B / F soit appliqué au premier étage, et ABCD au deuxième étage, l'entrée B sera la seule qui va à la sortie. Autrement dit, la sélection de l'une des huit entrées nécessite 5 bits dans le train binaire et utilise 5 emplacements de mémoire.

Multiplexeur d'entrée CLB

CLB. EFGH ABCD, . -, CLB 6 10 , , . , , , , . , , 6 , . , , .

Conclusion

Le XC2064 utilise une variété de réseaux hautement optimisés pour implémenter des blocs logiques et des interconnexions réseau. Ces chaînes doivent être étroitement emballées afin de s'intégrer dans le cristal. Même ainsi, le XC2064 était une très grosse puce, plus grosse que le microprocesseur de l'époque, et était difficile à fabriquer, coûtant des centaines de dollars. Comparé aux FPGA modernes, le XC2064 a un nombre absurdement petit de cellules, mais même cela a été le début d'une nouvelle ligne de produits révolutionnaire.

Deux concepts sont essentiels pour comprendre le flux binaire XC2064. Tout d'abord, le FPGA est implémenté sur la base de 64 tuiles, répétant des blocs qui combinent des blocs logiques et des interconnexions. Bien que le FPGA soit décrit comme ayant des blocs logiques entourés d'interconnexions, il n'est pas implémenté de cette façon. Le deuxième concept est que le train de bits n'est basé sur aucune abstraction, il mappe directement l'empilement bidimensionnel des cellules de mémoire FPGA. Ainsi, le flux binaire n'a de sens que si vous considérez la structure physique du FPGA.

Remarque

, XC2064 (. 11), CLB . , , 20% , . — -, . , . .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

J'ai annoncé mon dernier message sur Twitter, alors suivez kenshirriff . J'ai également un flux RSS . Merci à John McMaster, Tim Ansell et Philip Freidin pour les discussions.