introduction

Le registre à décalage de rétroaction linéaire (LFSR) est un registre à décalage de mots binaires, dans lequel la valeur du bit d'entrée est définie de manière unique par une fonction basée sur les valeurs des bits restants du registre avant le décalage. Le registre à décalage peut être une sorte de circuit électrique composé de composants discrets: transistors, résistances, il peut également être intégré dans un microcircuit ou implémenté dans un programme. L'ajout de rétroaction transforme le registre à décalage en un générateur de nombres pseudo-aléatoires, largement utilisé en cryptographie. Dans cet article, nous analyserons le principe de fonctionnement du RSLOS du matériel à ses différentes applications.

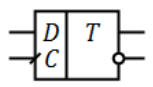

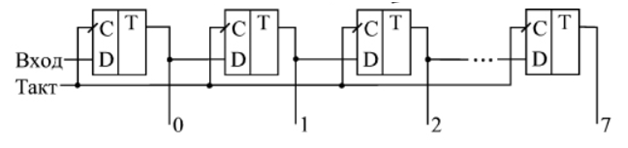

Un registre, en général, est un circuit constitué d'éléments de mémoire à un bit interconnectés. De tels circuits peuvent écrire, stocker, lire des données binaires de n bits. L'article traite d'une sorte de registre appelé registre à décalage. Le plus souvent, le registre à décalage est assemblé à partir de bascules D connectées en série, et le nombre de ces bascules est égal au nombre de bits n. Nous commençons cet article par les principes du D-trigger.

Déclencheur D

Abordons brièvement les bases. Globalement, l'électronique peut être divisée en deux sections: analogique et numérique. La principale caractéristique de la seconde est que les signaux sont définis par des niveaux de tension discrets. De plus, il n'y a que deux niveaux discrets. Ainsi, au lieu d'enregistrer la tension en volts, il suffit de nommer simplement l'un des deux niveaux discrets. C'est ainsi que les noms «zéro» et «un» apparaissent. En fait, ils définissent certains niveaux de tension, qui peuvent être n'importe quoi. Bien que, dans la plupart des cas, "zéro" signifie 0 Volts et "un" est 5 V, 3,3 V, 1,8 V, 1,5 V, etc. Ainsi, la phrase «à l'entrée zéro, à la sortie un» signifie: «à la tension d'entrée correspondant au niveau de zéro, à la tension de sortie correspondant au niveau un».

. , ? D- , ! .

– , .

D- – , . ,

D- , . : D (), C ( , , , clk, clock) Q (). : , , . , , .

. 1 - D-

D- : C, . . . - «», «», «».

|

|

||

(D) |

(Q) |

(D) |

(Q) |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

« ». , ( ) . , . , .. . , , . , .

, . D- . , . , , . D-, .

, n D-. . , , . .

? , , , . . «» . , , . ? ( ). . . , , , . . . , , . , : .

№ |

|

0 |

1 |

2 |

3 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

3 |

0 |

0 |

0 |

1 |

0 |

4 |

0 |

0 |

0 |

0 |

1 |

5 |

0 |

0 |

0 |

0 |

0 |

- . . ? , . . , , , , . .

hi - , . .

? . , , . , , 1 , . . . , .

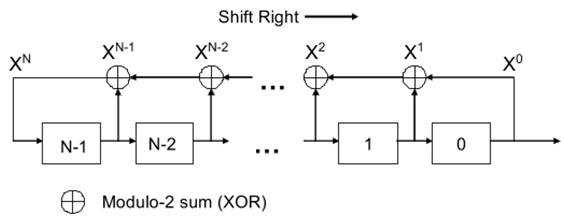

, . ? , , . n , n . , . Xi. , . . . N, Xi+N = Xi i. 2n-1, -. , , 2n-1. .

GF(2). . t + 1, (x) p:

Y(t) t. T – n :

, , . , GF(2) - : k 2k-1. . , . , . .

n |

LFSR-2 |

LFSR-4 |

2 |

2, 1 |

|

3 |

3, 2 |

|

4 |

4, 3 |

|

5 |

5, 3 |

5, 4, 3, 2 |

6 |

6, 5 |

6, 5, 3, 2 |

7 |

7, 6 |

7, 6, 5, 4 |

8 |

|

8, 6, 5, 4 |

, , . , n= 8 :

. : . . , . , , , . . : .

. . . . 2n1 , 2n2, . ., 2n1+n2+… , n1, n2, … .

. . . — 2017. — 117 .

. . . — , 2008. — 314 .

Eastlake D., Schiller J., Crocker S. Randomness requirements for security. — 2005. — 48 .