Paradigme

Il est assez important de souligner ici que le code machine doit ressembler, dans une perception subjective relativement fluide, à un pseudo-code dans les champs des tables de vidage et, le moins possible, donner l'ésotéricité de tous les champs de bits.

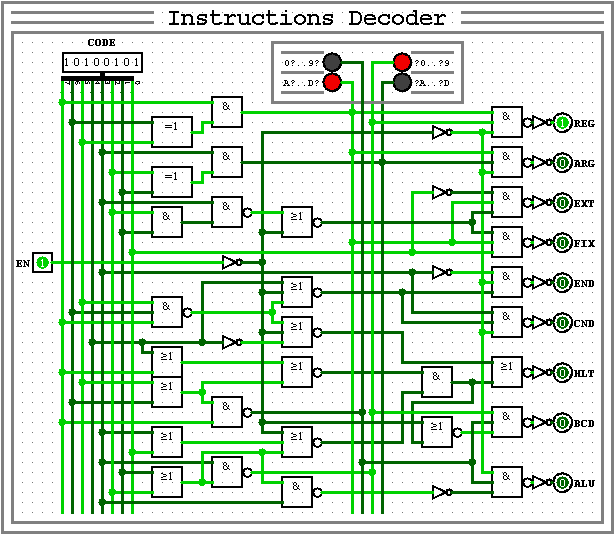

Décodeur de commande

L'un des éléments les plus importants et les plus clés de tout automate est un dispositif pour décoder exactement cette action à un certain moment que le programmeur lui-même avait à l'esprit lorsqu'il a composé l'ordre de ces commandes dans ses algorithmes.

Tout d'abord, il est nécessaire de faire un croquis du décodeur Koda-Koyaaniskatsi dans Logisim , en utilisant les éléments logiques les plus accessibles de la nomenclature de la série TTL produite afin d'assurer un assemblage facile du décodeur sur de vrais microcircuits.

Ici, nous proposons une désignation graphique conditionnelle pour le décodeur, qui est nécessaire pour assurer la compacité et la clarté de l'ensemble du circuit de la machine à l'avenir, ainsi que pour vérifier le bon fonctionnement du décodage des 256 codes d'instructions.

Registres de préfixes intemporels

Lorsque les tests visuels des performances du décodeur se sont bien déroulés et sans échecs visibles, il était temps de connecter les principaux registres pour stocker les index des RON actifs, qui sont déclenchés par les commandes du groupe REG comme préfixes architecturaux.

Pour assurer le stockage des vecteurs de routage des données par les instructions ALU et RAM, un registre supplémentaire et deux multiplexeurs liés sont ajoutés, avec lesquels vous pouvez lier des registres arbitraires de n'importe quel groupe en tant qu'opérandes d'instructions.

En eux-mêmes, ces registres ne sont pas destinés à stocker les résultats des calculs et jouent une sorte de rôle de pointeurs vers les registres requis afin de fournir une interaction contrôlée dans le programme entre tous les RON et / ou la mémoire disponibles.

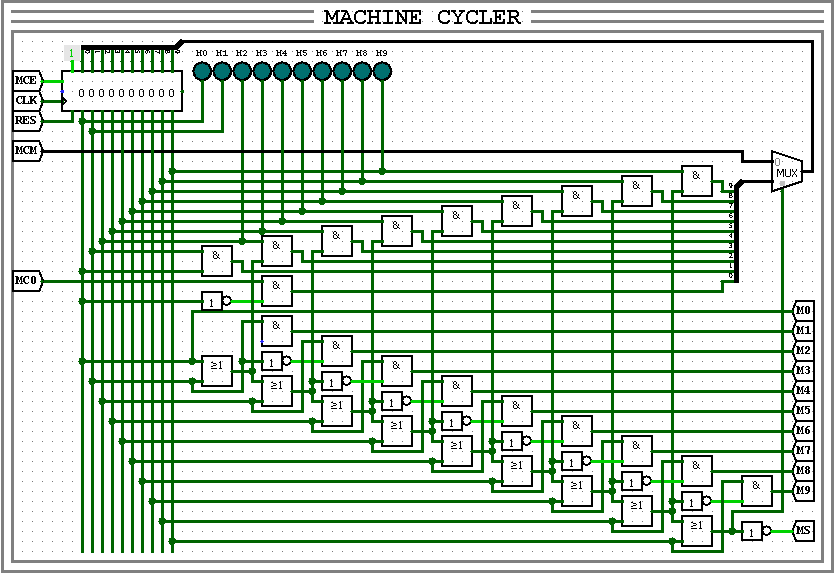

État architectural

Assurer l'interaction normale du programme de tous les registres nécessite la présence d'un fichier de registre à deux ports, qui n'est pas inclus dans les bibliothèques Logisim, ce qui nous oblige à rechercher d'autres solutions alternatives plus ou moins coûteuses. Le Koyaaniskatsi classique a un fichier de registre assez complexe, qui n'est pas considéré ici comme un exemple illustratif et nécessite le développement d'une nouvelle solution pour organiser un fichier de registre multi-cycle avec un accès lent. Comme le circuit s'est avéré être un cycle, il est assez difficile d'organiser le fichier de registre dans la RAM ici et il devient nécessaire de construire un circuit multi-cycle avec de nombreux cycles spéciaux se remplaçant dans un ordre strictement spécifié.

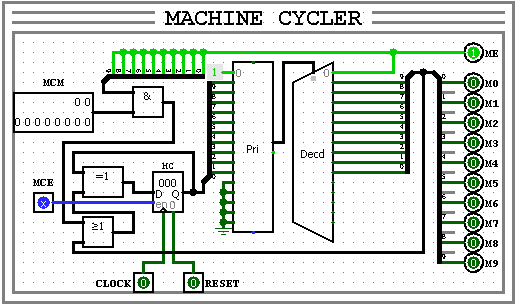

L'expression algorithmique du compteur de cycles peut être décrite comme "m & = m - 1" avec désactivation séquentielle de tous les bits actifs de l'état architectural, où à un certain moment du cycle machine seuls les nœuds clés du circuit sont activés.

Le prototype au maximum étendu du compteur de cycles de la machine peut être représenté sur un croquis d'un circuit similaire, ce qui est assez difficile à comprendre la logique de son fonctionnement.

Une esquisse similaire peut être l'option la plus optimale et la plus polyvalente:

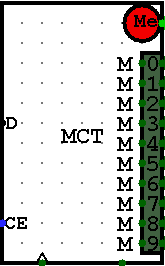

et pour une utilisation dans un schéma, une désignation graphique conditionnelle peut être la suivante:

A l'aide de portes logiques à 3 OU, il est désormais possible de traduire le signal de chacune des commandes dans le masque binaire des cycles nécessaires à la bonne exécution de la commande, pendant toute la durée d'exécution dont le compteur de commandes sera temporairement suspendu.

Conclusion

Ainsi, comme vous pouvez le voir, pour au moins plus ou moins commencer à comprendre les nuances de la construction indépendante d'une machine programmable, il nous suffit de nous débrouiller avec des connaissances de base, même au niveau du dessin du schéma d'une guirlande d'arbres de Noël clignotante. Aucun matériel de référence connu de tout le monde n'a été délibérément utilisé ici, de sorte que le processus de création était plus excitant et exempt de toutes tendances et tendances mondiales, sans prêter attention à toutes les erreurs de calcul ou erreurs possibles.

Dans la partie suivante, je vais essayer de continuer ma construction pas à pas du "processeur akyn",

puisque le nouveau projet fonctionne presque pour moi, mais j'ai décidé de le redessiner à partir de zéro,

et en même temps de documenter toutes les étapes clés ...