IBM a annoncé le développement d'une technologie de processus 2 nm.

Ce qui a été annoncé:

- 2 nm.

- 50 milliards de transistors dans une zone de la taille d'un clou. Plus tard, ils ont clarifié - sur une superficie de 150 mm2 - soit 333 millions de transistors par millimètre carré (

- MTx / mm 2 ).

- Le pas de grille du transistor (Contacted Poly Pitch, CPP) est de 44 nm, la longueur de grille est de 12 nm.

- (Gate All Around, GAA). – , IBM (horizontal nanosheets, HNS).

- HNS .

- 45% 75% 7 .

- (EUV) HNS 15 70 . , SRAM.

- 5 .

S'agit-il vraiment d'une technologie de processus 2 nm? Aujourd'hui TSMC est le leader de la production de puces. Nous avons tracé la relation entre les noms de processus TSMC et la densité des transistors en approximant la courbe avec un coefficient de détermination de 0,99.

De 28 nm à 5 nm, les chiffres réels sont utilisés selon IC Knowledge et TechInsights. Les chiffres 3 nm sont basés sur les communiqués de presse TSMC. 2 nm et 1,5 nm est notre extrapolation.

À l'aide du graphique, vous pouvez convertir la densité des transistors en une technologie de processus TSMC équivalente (TSMC Equivalent Node ou TEN). On obtient 2,9 nm pour 333 MTx / mm 2 . De notre point de vue, il s'avère qu'il s'agit d'une technologie de processus à 3 nm et non à 2 nm.

Pour comparer plus en détail l'annonce d'IBM avec les annonces précédentes de la technologie de processus 3 nm et du processus 2 nm proposé, plusieurs hypothèses doivent être faites.

- On sait d'après l'annonce que le CPP est de 44 nm.

- Supposons que la production utilise la technologie de placement de transistor la plus étroite, Single Diffusion Break (SDB).

- D'après la photo en coupe de l'annonce, la technologie Buried Power Rails (BPR) n'est pas utilisée. Le BPR est nécessaire pour réduire la taille de la piste HNS à 5,0 - supposons donc que cette valeur est de 6,0 dans ce processus.

- Pour atteindre une densité de 333 MTx / mm 2 , le pas minimal du métal devrait être de 18 nm - une valeur très agressive qui nécessiterait probablement une photolithographie multi-matrice EUV.

IBM 2 nm par rapport à la technologie de processus 3 nm existante

Le tableau suivant compare les conceptions IBM avec nos estimations de processus 3 nm de Samsung et TSMC. Nous savons que Samsung travaille également avec HNS et TSMC a opté pour un FinFET 3 nm. Samsung et TSMC ont également annoncé une augmentation de 3 nm de la densité des transistors pour leur technologie de processus par rapport à 5 nm. Par conséquent, la densité des transistors des trois sociétés nous est connue et nous pouvons calculer le TEN pour tous. Le TEN d'IBM est de 2,9; on peut voir que Samsung a 4,7 et TSMC a 3,0. Encore une fois, il s'avère que 2 nm d'IBM est plus similaire à 3 nm de TSMC, alors que Samsung est à la traîne.

Les paramètres indicatifs nécessaires pour atteindre les densités annoncées sont surlignés en rouge, en supposant que toutes les entreprises utilisent la technologie SDB. La hauteur des pistes est la plus petite dans TSMC, car sans BPR dans FinFET, ce paramètre peut atteindre 5,0, cependant, pour que le HNS ait la même hauteur, BPR doit être utilisé.

IBM 2 nm par rapport à la technologie de processus 2 nm existante

Dans le tableau suivant, nous avons estimé les valeurs des paramètres pour la technologie de processus 2 nm de Samsung et TSMC. Dans notre extrapolation, nous supposons que les entreprises utilisent le BPR (la technologie BPR n'est pas encore mature, mais sera probablement mise en service lorsqu'elles annoncent un processus de 2 nm en 2023-2024). Supposons également que les entreprises adoptent l'architecture NHS forksheet (HNS FS) pour atteindre une hauteur de voie de 4,33. Les estimations du RPC et du MPP sont fondées sur les tendances actuelles de la miniaturisation de la technologie.

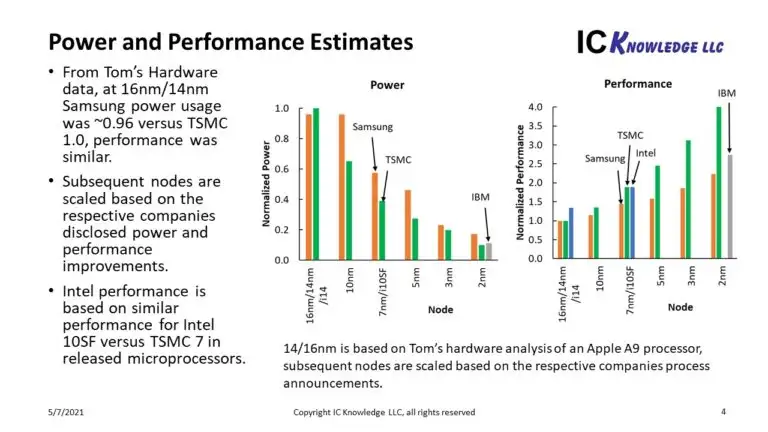

Consommation d'énergie et performances

Cette année, j'ai déjà fait des suppositions sur la consommation d'énergie et les performances des appareils Samsung et TSMC en utilisant des données de performances supplémentaires d'Intel. L'extrapolation est basée sur les assurances des entreprises et sur des comparaisons dans le monde réel entre les processus 14 nm et 16 nm.

Étant donné qu'IBM a comparé les améliorations de la consommation d'énergie et des performances aux processus de fabrication 7 nm avancés, je peux tracer leurs données sur les mêmes graphiques.

Grâce à l'utilisation de HNS, IBM a réalisé d'importantes économies d'énergie, rendant son processus 2 nm plus efficace que le processus 3 nm de Samsung et TSMC. Même si, à notre avis, lorsque TSMC passera au HNS à 2 nm, leur consommation électrique ne sera pas inférieure à celle d'IBM. En termes de performances, nous supposons que le processus 3 nm de TSMC devancera le processus 2 nm d'IBM.

Bien entendu, ce ne sont que des estimations basées sur un grand nombre d'hypothèses.

Conclusion

Après avoir analysé l'annonce d'IBM, nous arrivons à la conclusion que leur technologie de processus 2 nm est plus similaire à la technologie de processus 3 nm de TSMC en termes de densité de transistors, tout en ayant les meilleurs indicateurs de consommation d'énergie, mais inférieurs en vitesse. La déclaration d'IBM est impressionnante - cependant, il ne s'agit que d'un échantillon de laboratoire, dépassant clairement les 3 nm de TSMC uniquement en termes de consommation d'énergie. Dans le même temps, les premiers lots à risque d'appareils 3 nm de TSMC apparaîtront cette année, et les lots commerciaux l'année prochaine.

À notre avis, TSMC conservera l'avantage en termes de densité, de consommation d'énergie et de vitesse des appareils basés sur la technologie de processus 2 nm lorsqu'ils entreront en production en 2023-2024.