Plus récemment, je suis tombé sur l'une des options pour une carte de débogage avec SoC Zynq XC7Z020. Après avoir cherché sur Internet des matériaux, un guide pratique, et essayé de lancer mon projet minimal, j'ai découvert qu'il y avait un certain nombre de pièges. C'est ce dont je voudrais parler dans l'article. Qui s'en soucie - bienvenue au chat.

Important! Avant de commencer l'histoire, j'aimerais faire une réservation à l'avance que l'objectif principal que je poursuis en écrivant cet article est de montrer aux amateurs par où commencer lorsqu'ils étudient les tableaux de débogage basés sur Zynq. Je ne suis pas un développeur professionnel pour FPGA et SoC Zynq et je peux faire des erreurs dans l'utilisation de la terminologie, n'utiliser pas les moyens les plus optimaux pour résoudre les problèmes, etc. Mais toute critique constructive et bien motivée n'est que la bienvenue. Eh bien, allons-y ...

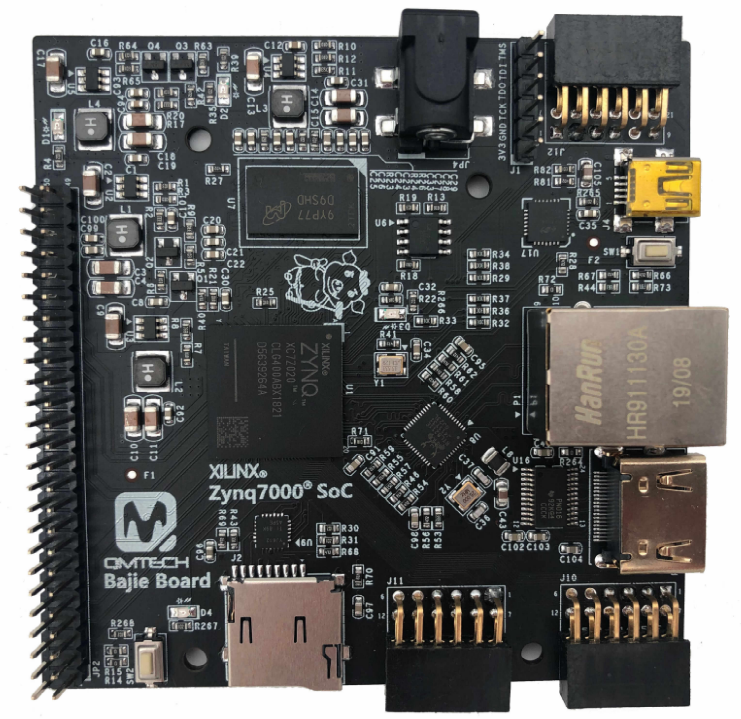

De quel type de débogage s'agit-il? Montrer-dire ...

Pendant très longtemps, j'ai voulu jouer avec SoC Zynq, mais mes mains ne pouvaient pas l'atteindre. Mais encore une fois sur Google - j'ai vu que le débogage avec Zynq à bord, de QMTech, est vendu à un prix tout à fait raisonnable, il s'appelle Bajie Board. Debug est disponible en plusieurs versions avec différentes saveurs Zynq SoC. J'ai choisi la version XC7Z020 pour moi-même et l'ai immédiatement commandée.Après quelques semaines, je l'avais déjà entre les mains.

, . , 5/2, mini-USB microSD Flash- SanDisk 16 Linux. , , USB-, Putty mini- Embedded Linux. Linux Zynq, , , ...

, -:

SoC: XC7Z020-1CLG400C

(datasheet:https://www.xilinx.com/support/documentation/data_sheets/ds190-Zynq-7000-Overview.pdf);

33,333 ;

DDR3 512 Micron, MT41K256M16TW-107:P;

micro SD;

FPGA TPS563201 ( 4.5V 17V, 3A);

50- Digilent PMOD , , 2,54 . ( , );

(PS);

RGMII Ethernet- Realtek RTL8211E-VL, PS;

, (PL) (PS);

HDMI- TI TPD12S016;

JTAG-;

.

, , - JTAG-. .

, Xilinx Vivado Xilinx SDK. , , Vivado . Xilinx SDK ( Vitis) .

YouTube Vivado 2019.1 ( - , Xilinx SDK) - , 2020.2.

Xilinx Zynq - Xilinx, . , , Vivado - 2020.2, 2020.3 .. Versal SoC, Zynq.

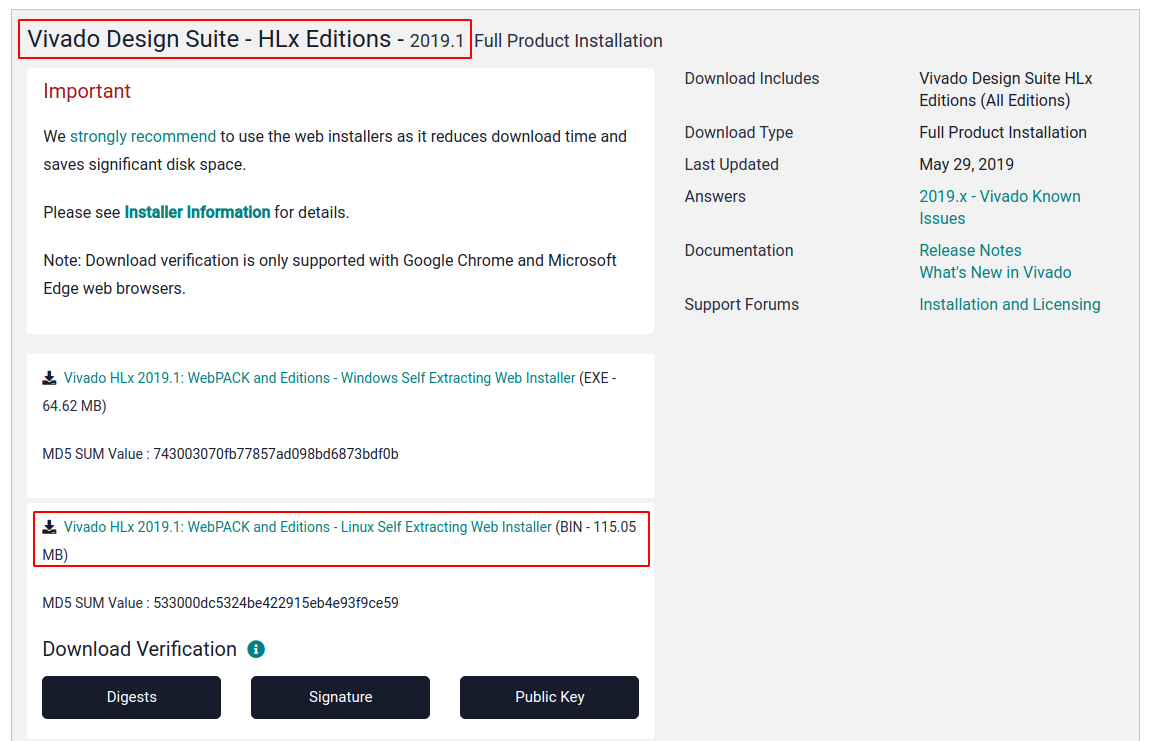

, .. Linux - Vivado Archive - 2019.1 Vivado HLx 2019.1: WebPACK and Editions - Linux Self Extracting Web Installer Vivado Design Suite - HLx Editions - 2019.1. Windows - Windows Self Extracting Web Installer.

, :

chmod +x ~/Downloads/Xilinx_Vivado_SDK_Web_2019.1_0524_1430_Lin64.bin ~/Downloads/Xilinx_Vivado_SDK_Web_2019.1_0524_1430_Lin64.bin

.

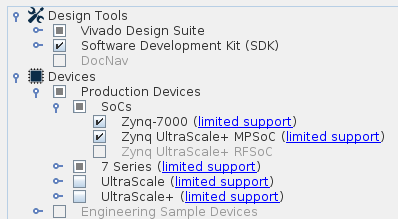

, ;

;

Vivado HL WebPACK;

, SoC Zynq .

16 -, .

Vivado JTAG-. Linux :

cd Xilinx2019.1/Vivado/2019.1/data/xicom/cable_drivers/lin64/install_script/install_drivers/

sudo ./install_drivers

6 JTAG- . :

cd ~/Xilinx2019.1/Vivado/2019.1/bin

./xsdb

xsdb% connect -host localhost

xsdb% jtag targets

1 Platform Cable USB 13724327082b01

2 arm_dap (idcode 4ba00477 irlen 4)

3 xc7z020 (idcode 23727093 irlen 6 fpga)

.

Hello, world “ ”

LED- .

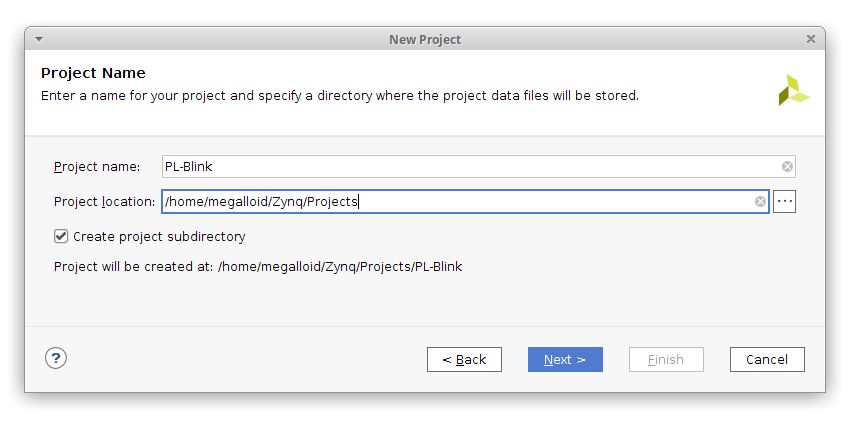

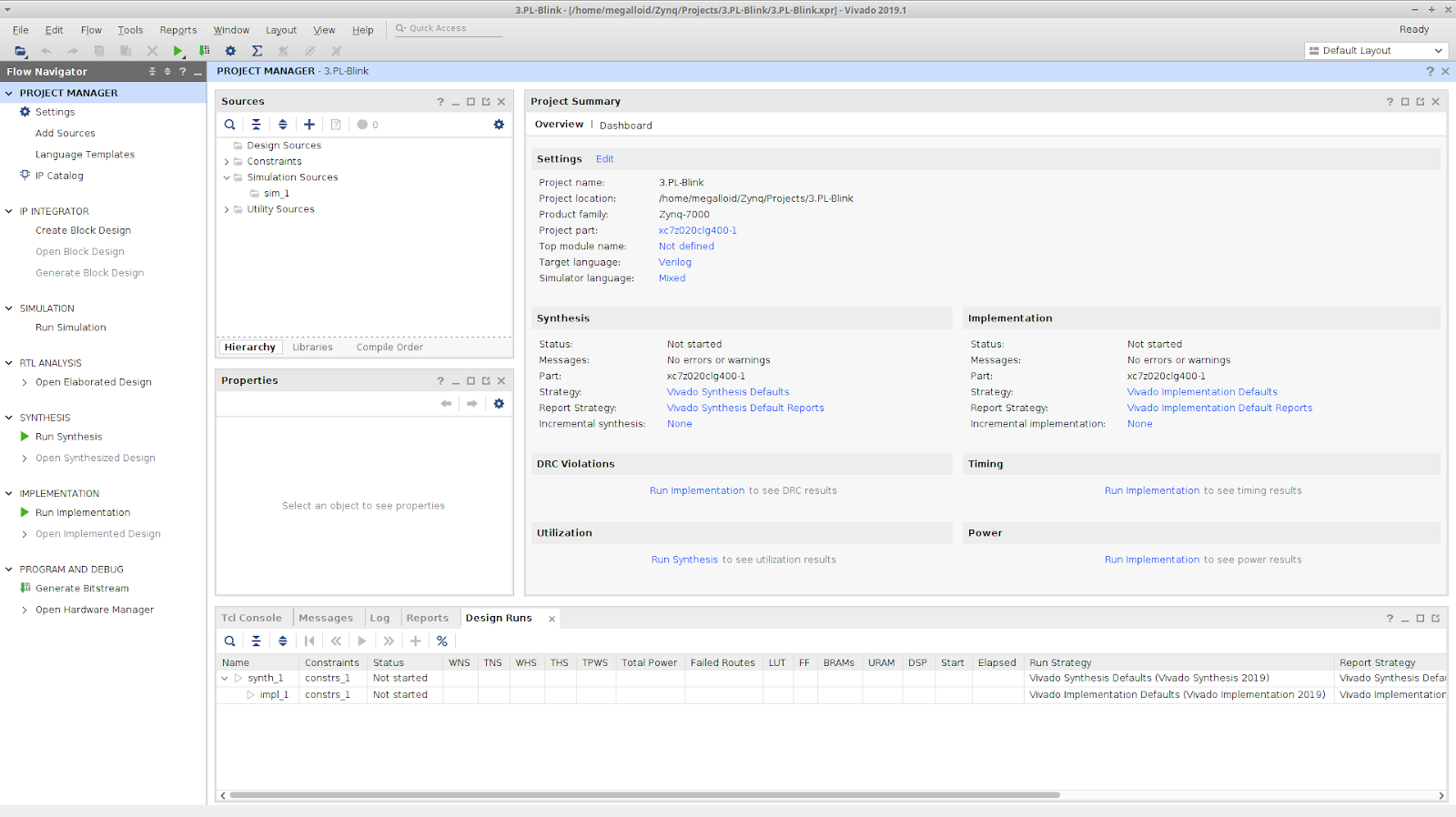

Vivado . File - Project - New…

, Next > PL-Blink.

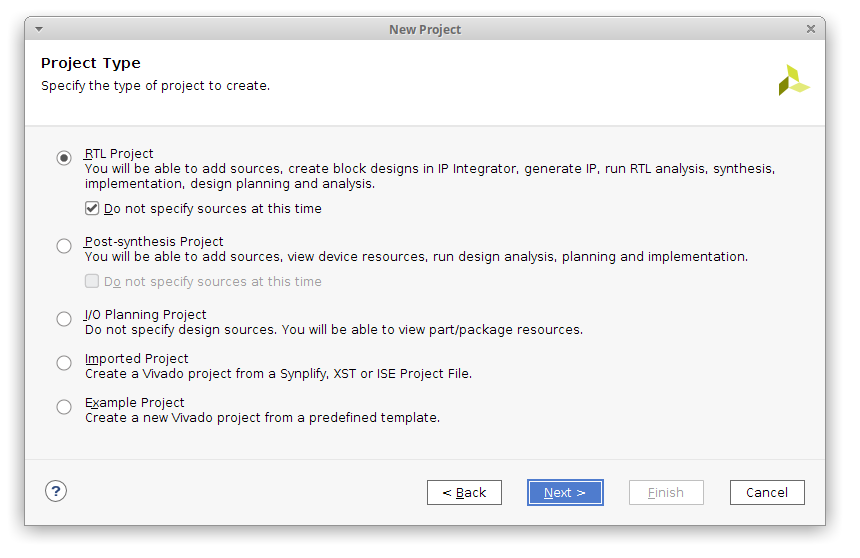

RTL Project Do not specify sources at this time.

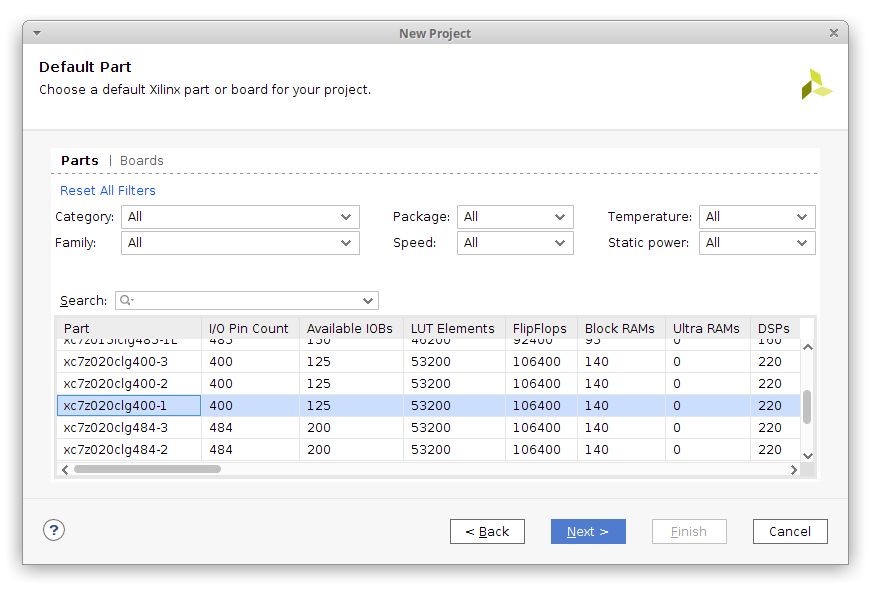

xc7z020clg400-1.

Finish.

Vivado !

, , , =)

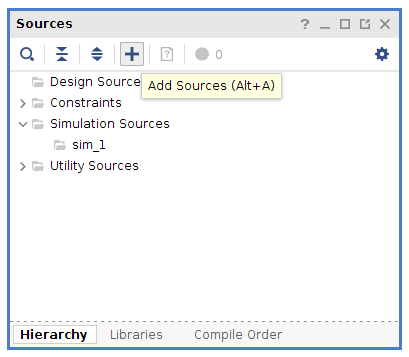

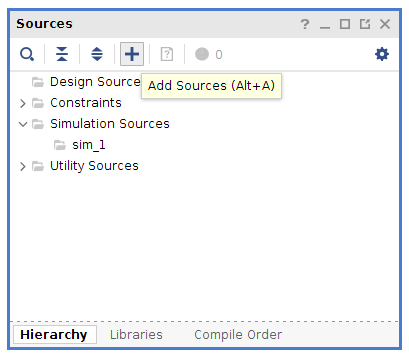

Sources Add Sources.

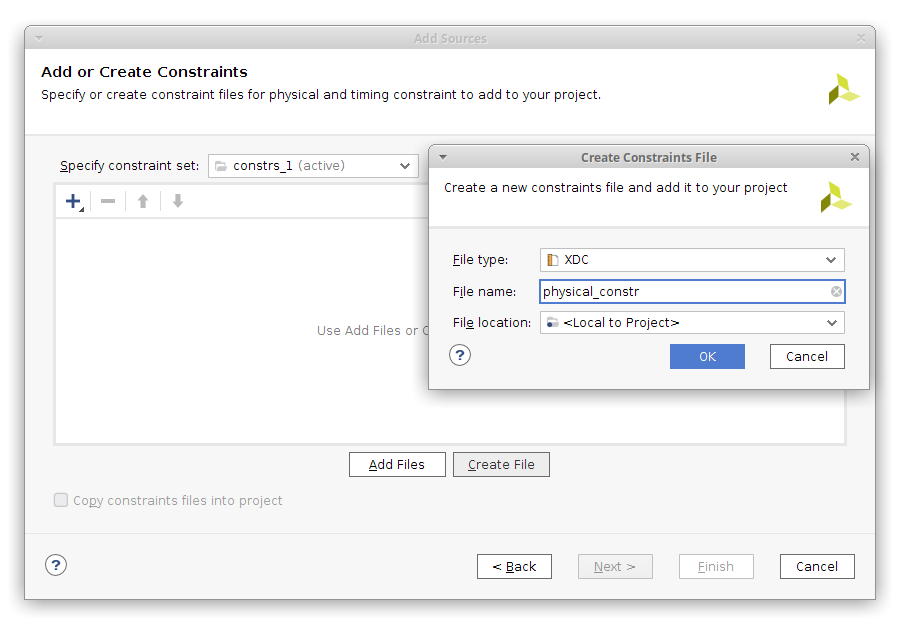

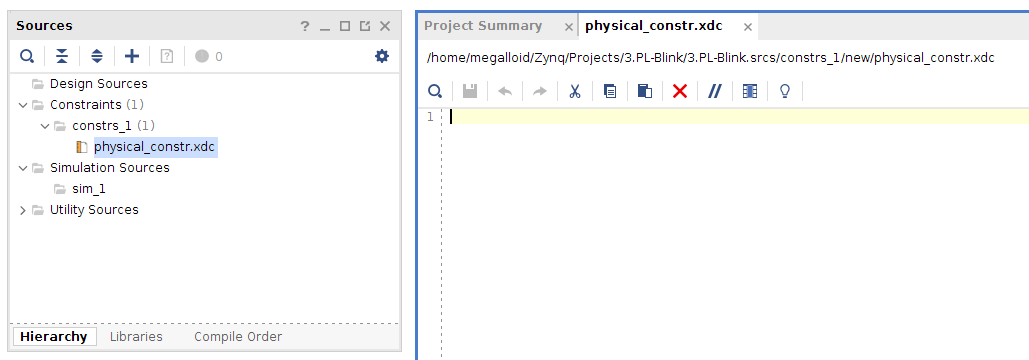

Add or create constraints.

Create file physical_constr. .

Finish Soures :

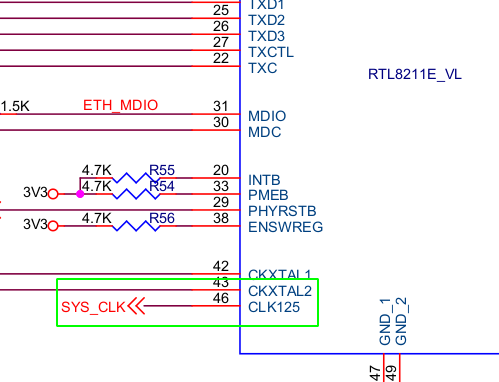

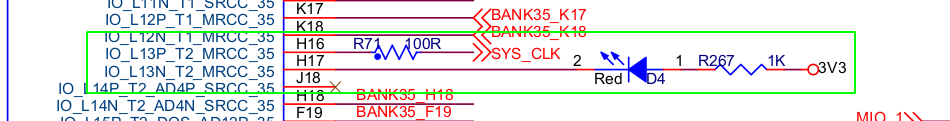

, , . , , Ethernet- RTL8211E-VL PLL, 125 H16 (IO_L13P_T2_MRCC_35). ? =)

, .

, , H17 (IO_L13N_T2_MRCC_35) , .

. constraints- :

# User LED and Clock

set_property IOSTANDARD LVCMOS33 [get_ports led_h17_d4]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN H17 [get_ports led_h17_d4]

set_property PACKAGE_PIN H16 [get_ports sys_clk]

, , , , .

, get_ports ( ). , Verilog-.

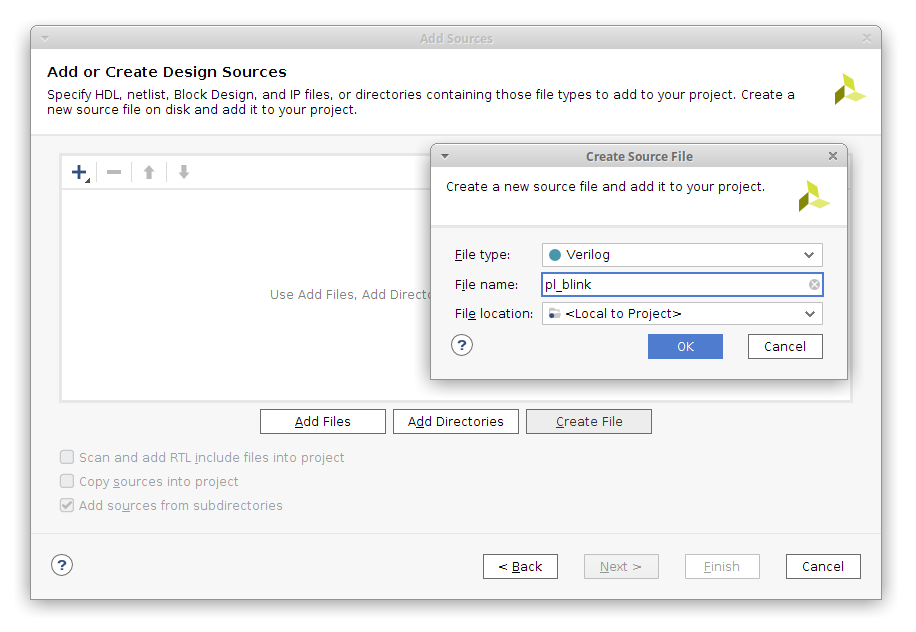

Design Source. Sources Add Sources.

Add or create design sources. Create File, , Verilog. Finish.

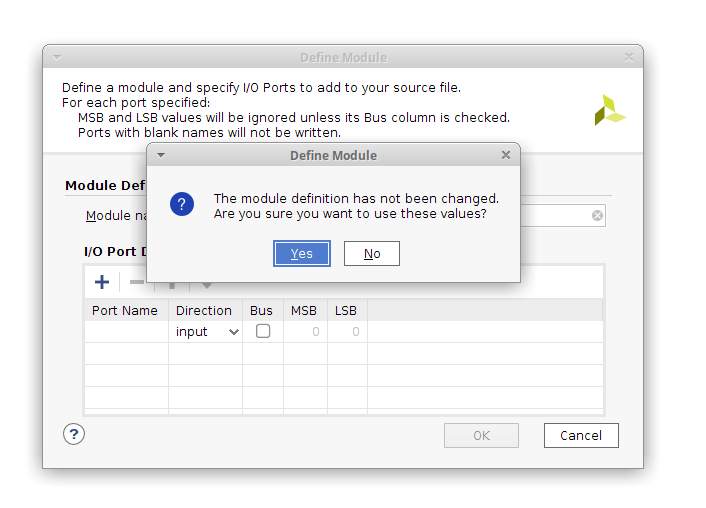

Yes.

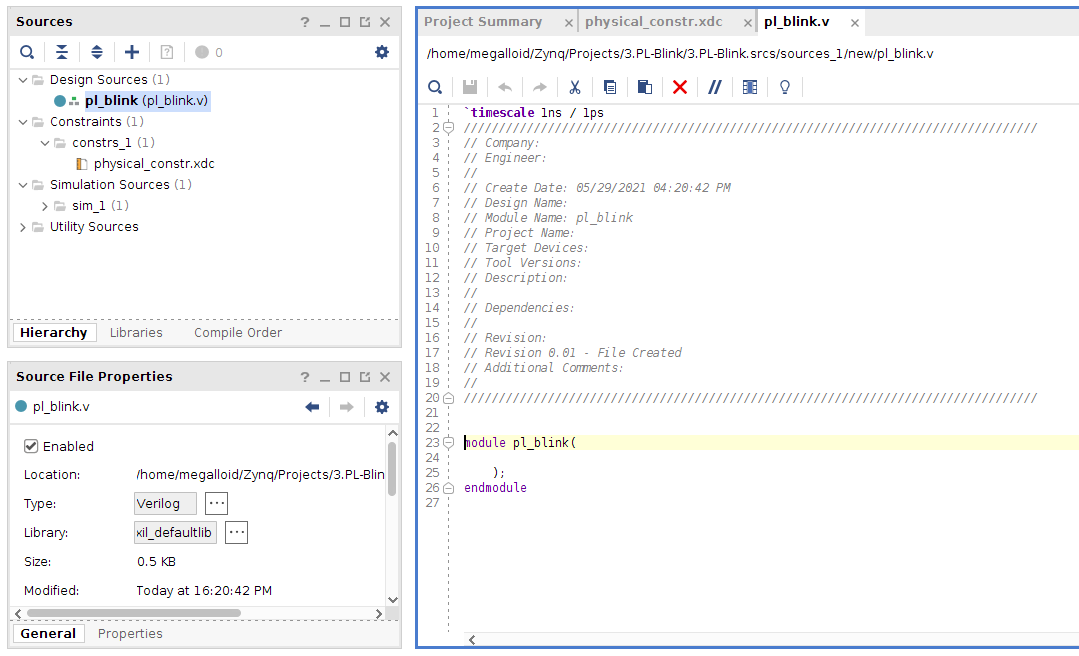

:

Verilog- :

// , Verilog.

// , .

`timescale 1ns / 1ps

// - ( ++)

module pl_blink(input sys_clk, output led_h17_d4);

//

reg r_led;

// ,

reg [31:0] counter;

//

initial begin

counter <= 32'b0; //

r_led <= 1'b0; //

end

// ,

always@(posedge sys_clk)

begin

counter <= counter + 1'b1; //

if(counter > 12000000) //

begin

r_led <= !r_led; //

counter <= 32'b0; //

end

end

assign led_h17_d4 = r_led; // ()

endmodule

Ctrl + S . , . - , Zynq .

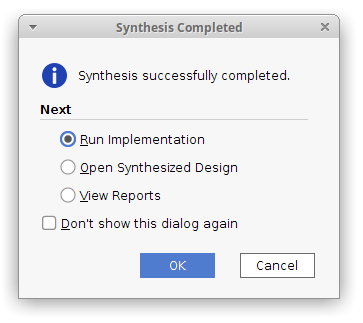

Run Synthesis . , :

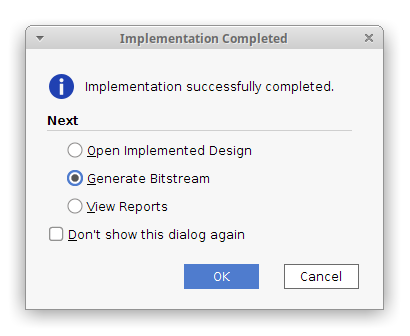

Run implementation . Generate Bitstream :

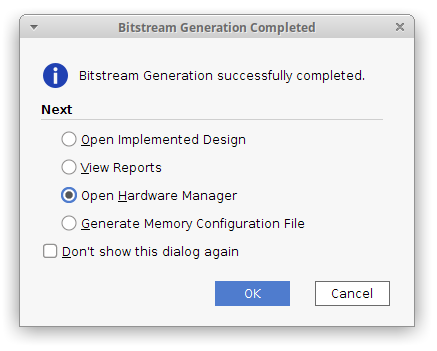

, , Open Hardware Manager :

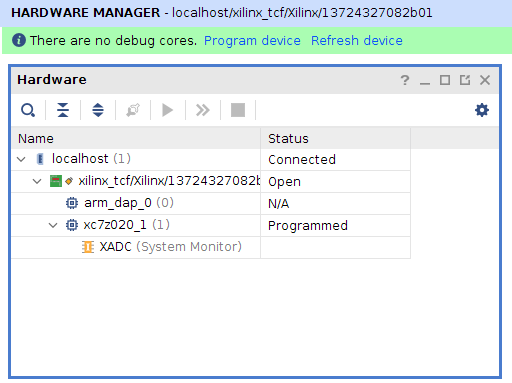

Hardware Manager Auto connect, :

Dans le menu de gauche ou en cliquant avec le bouton droit de la souris sur xc7z020_1 dans le menu Matériel , cliquez sur l'élément Program Device .

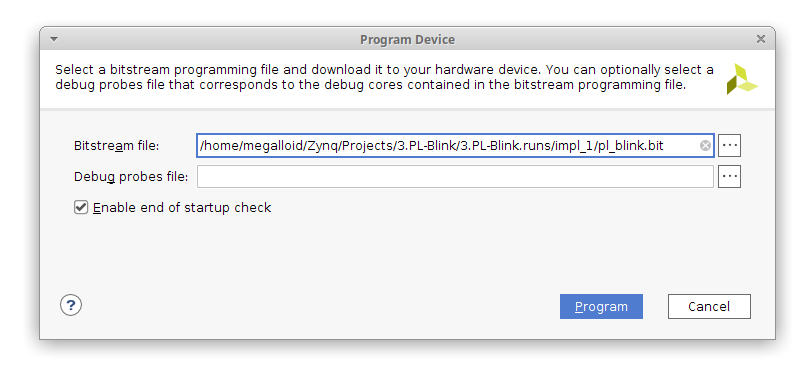

Dans la fenêtre suivante, assurez-vous que le chemin d'accès au fichier bitstream est correctement spécifié et cliquez sur le bouton Programmer.

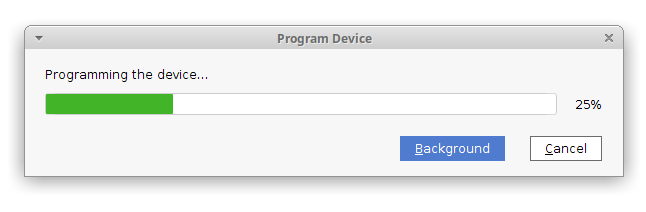

Le programme est téléchargé sur notre tableau ...

Et après un moment, la LED D2 sur la carte s'allume, ce qui nous informe que «FPGA DONE» et à l'autre extrémité de la carte, nous voyons une LED clignotant joyeusement. =)

En général, la tâche peut être considérée comme terminée. Je pense qu'en maîtrisant le langage Verilog et en résolvant tout nouveau problème en utilisant cette carte, je pourrai à nouveau vous plaire.