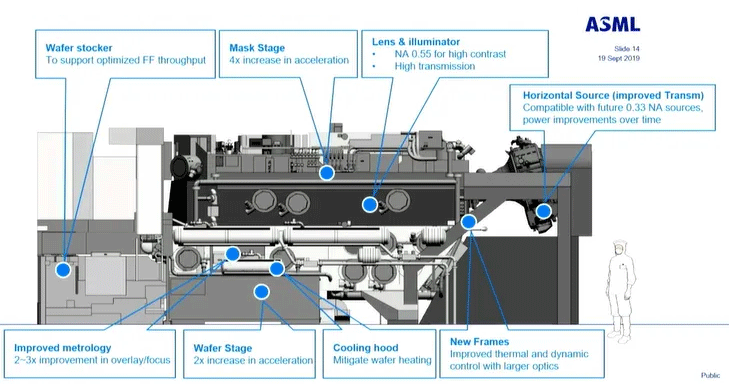

Futur scanner ASML à haute ouverture numérique 0,55 (high-NA EUV) d'une valeur d'environ 300 millions de dollars Source : Présentation ASML

La société néerlandaise ASML détient le monopole des équipements de photolithographie dans l'ultraviolet profond (EUV) avec une marge de leadership technologique pour plusieurs années à venir des concurrents... Par conséquent, le retard dans la prochaine génération de scanners n'affectera pas les bénéfices de l'entreprise, les sources disent Seeking Alpha. Au contraire, ASML gagnera encore plus d'argent en vendant des équipements de génération actuelle.

Certains experts pensent que dans la situation actuelle, il n'y a pas du tout de temps pour les mises à niveau. Le déficit est si fort que certains fabricants, au contraire, reprennent la production de microcircuits de l' ancien générations auparavant abandonnées.

Mais c'est la situation du marché. À l'avenir, TSMC et Samsung prévoient bien sûr d'améliorer le processus technologique. La seule question était : mettre en œuvre les projets suivants sur l'équipement actuel avec sa mise à niveau vers le multipatterning (plusieurs opérations séquentielles de lithographie et gravure à travers plusieurs photomasques avec une diminution des nœuds à 5/3 nm) - ou attendre un nouveau système EUV avec un modèle à 3/2 nm.

L'instrument actuel pour la lithographie ultraviolette profonde est ASML NXE : 3400C, et le scanner de lithographie EUV à haute NA de prochaine génération sera ASML EXE : 5000. Il sera équipé d'une toute nouvelle optique 0,55 NA, qui réduira considérablement la taille des éléments de gravure sur la plaquette de silicium.

La façon dont l'ouverture numérique et la résolution sont calculées sont deux des principales caractéristiques d'un scanner. Source : présentation ASML

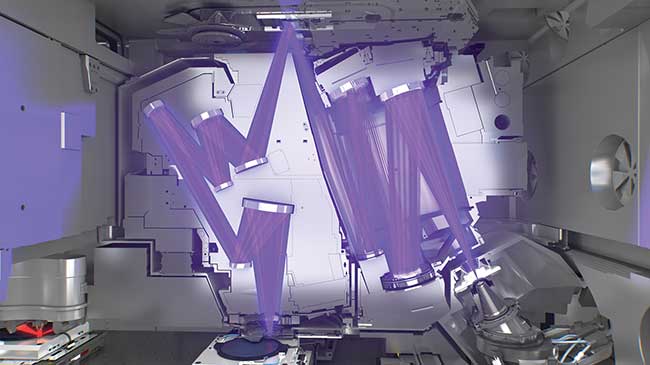

Trajectoire d'impulsion lumineuse du laser (en bas à droite) au dispositif d'éclairage, masque avec topologie cristalline par optique de projection sur plaquette de silicium dans un véritable scanner ASML.

Le problème est maintenant « résolu ». La transition vers de nouveaux équipements est reportée à 2025 ou 2026. Ces systèmes se sont avérés trop compliqués et coûteux en production, écritA la recherche d'Alpha. Pour rappel, les véhicules de 180 tonnes, de la taille d'un bus à impériale, témoignent à eux seuls de la complexité logistique de l'industrie électronique. Les composants sont fabriqués par environ 5 000 fournisseurs. Par exemple, l'Allemand Carl Zeiss produit des lentilles. Dutch VDL - manipulateurs robotiques qui alimentent les plaques dans une machine. Les sources lumineuses sont fabriquées par la société américaine Cymer, rachetée par ASML en 2013.

Selon les témoignages, un scanner EUV à haute NA coûtera environ 300 millions de dollars (les scanners ASML de la génération actuelle coûtent environ 180 millions de dollars chacun). Il deviendra peut-être l'appareil industriel le plus cher de l'économie mondiale.

Il n'y a absolument rien de mal avec la latence d'ASML EXE : 5000 scanners. Des microcircuits de 3 nm pourraient être produits sur de nouveaux équipements, mais maintenant, peut-être, ils le seront sur d'anciens scanners - en plusieurs passes et en utilisant d'autres architectures. Et les scanners de nouvelle génération utiliseront des puces de 2 nm.

L'équipement EUV actuel pour puces 7 et 5 nm utilise un système optique 0,33 NA et une à deux expositions lithographiques. À un moment donné, la double passe semblait facile. Aujourd'hui, on craint de plus en plus que le modèle double EUV soit trop complexe et coûteux pour de nombreux appareils. Et à 3 nm, un triple passage peut être nécessaire, ce qui est encore plus difficile.

Photolithographie en ultraviolet profond

Au fil des ans, les fabricants de puces ont systématiquement réduit la taille des nœuds de 30 % par génération, réduisant ainsi le coût de chaque transistor. À son tour, cela a permis de produire des processeurs plus puissants. Le cycle battait régulièrement tous les 18 mois environ.

La fabrication a été simple jusqu'à la marque des 20 nm lorsque les transistors plats ont heurté le mur. À partir de 2011, les fabricants de puces sont passés aux transistors à grille verticale (FinFET) 22 nm et 16/14 nm.

Les FinFET sont plus rapides et nécessitent moins d'énergie, mais sont difficiles et coûteux à fabriquer. Ainsi, le temps de transition vers de nouveaux nœuds est passé de 18 mois à 2,5 ans.

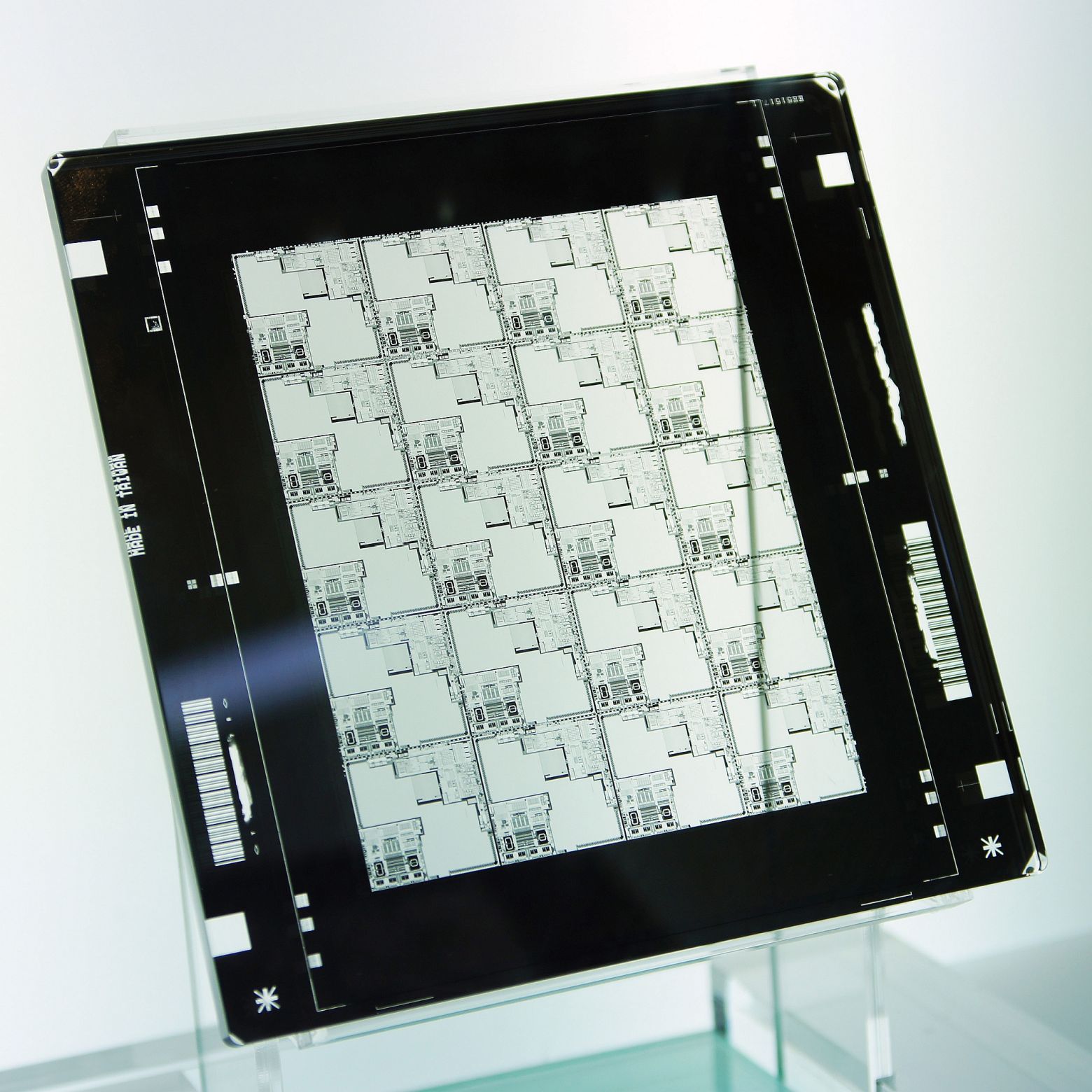

La lithographie a également rencontré des difficultés. Le processus de lithographie commence par un photomasque.

Photomasque

En usine, le photomasque est placé dans le scanner. Il projette de la lumière à travers le masque sur la plaque, créant des motifs dessus, qui sont ensuite gravés à l'acide. Il s'agit d'un processus simple avec une taille de pas de 28 nm, mais déjà à partir de 20 nm, les pièces deviennent trop denses, ce qui rend difficile l'impression d'éléments individuels sur la plaquette.

Photomasque réaliste avec correction optique de proximité. Auteur : LithoGuy

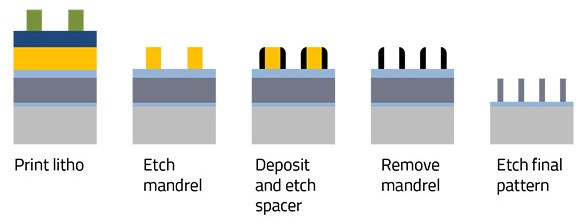

Par conséquent, les fabricants de puces sont passés au multipatterning, où la conception originale est divisée en deux ou plusieurs photomasques « clairsemés ». Pour appliquer ces éléments à la plaquette, les fabricants de puces utilisent une variété de conceptions de processus en usine, y compris une entretoise auto-alignée et un double motif.

Les entretoises à alignement automatique empêchent le masque de se déplacer. Source : Lam Research La

double réticulation augmente la densité. Source : Lam Research

Le scanner ASML le plus avancé NXE : 3400C utilise une longueur d'onde de 13,5 nm et un système optique de 0,33 NA. L'alimentation de 246 watts fournit un débit de 170 plaquettes par heure (WPH).

Samsung, TSMC et Intel passent progressivement aux nœuds technologiques 7 et 5 nm utilisant les scanners ASML NXE : 3400C. D'après les informations disponibles , dans la technologie des procédés de 7 nm, une passe avec un pas de 40 nm suffit, mais déjà dans les puces de 5 nm, le même TSMC utilise un pas de 30 nm, ce qui est proche de la limite physique à cette ouverture .

Qu'est-ce que la haute NA ?

Bien que la double réticulation soit encore possible pour 5 voire 3 nm, c'est la limite pour les semi-conducteurs à grille verticale. Ensuite, vous devez maîtriser les transistors à nanofeuillet (nanofeuille FET).

Transistors nanofeuilles Les

nouveaux scanners ASML à haute ouverture numérique (high-NA), permettant d'augmenter la résolution de l'image sur un photomasque, sont indispensables.

L'ASML a annoncé lors de la conférence de janvier qu'elle retardait la mise en œuvre de la nouvelle version d'EUV d'au moins trois ans. Auparavant, il était prévu de maîtriser la technologie d'ici 2023, et maintenant les plans sont reportés à 2025 ou 2026.

Selon les connaisseurs, un certain nombre d'améliorations technologiques sont nécessaires pour maîtriser la technologie de processus à haute NA. L'industrie y travaille, mais il y a plusieurs facteurs inconnus ici.

Ces dernières années, les fabricants de puces ont travaillé en parallèle sur d' autres architectures d'emballage de puces (2.5D, 3D-IC, etc.) pour faire évoluer les puces, même en cas de latence NA élevée.

Soit dit en passant, le retard actuel à NA élevé rappelle la façon dont l'industrie est restée longtemps bloquée sur la lithographie par immersion 193 nm, ce qui a finalement stimulé les ventes d'équipements. Du point de vue de l'activité ASML, il n'y a donc aucun problème : l'entreprise gagnera plus d'argent avec la première génération d'EUV. Il est également entré sur le marché avec de longs retards et rien de terrible ne s'est produit.

L'introduction des scanners ASML NXE : 3400C a commencé en 2020. Parmi les trois principaux fabricants TSMC, Samsung et Intel, les deux premiers sont en tête dans l'utilisation des derniers équipements ASML pour la photolithographie ultraviolette profonde, et Intel prévoit de passer à la lithographie EUV seulement à la fin de 2022.