Il est à noter que les structures MOS fonctionnent toujours, étant considérablement réduites, alors que la plupart des choses ne peuvent pas être simplement réduites comme ça. Par exemple, vous ne pouvez pas mettre à l'échelle un moteur 10 fois et vous attendre à ce qu'il fonctionne. La plupart des objets physiques souffrent de la loi du carré-cube : l'aire d'un objet se développe comme un carré de taille linéaire et son volume comme un cube. Cependant, dans le cas des structures MOS, la plupart des composants lors de la mise à l'échelle restent inchangés ou s'améliorent (par exemple, la fréquence et la consommation d'énergie). Pour plus de détails sur la mise à l'échelle, consultez le livre de Mead et Conway, Introduction to VLSI Systems.... Ironiquement, le livre de 1978 affirme que la mise à l'échelle a une limitation fondamentale d'un quart de micron (250 nm) sur la longueur du canal en raison des propriétés physiques de la matière. Cette limitation s'est avérée incroyablement imparfaite - maintenant, les transistors passent à la taille caractéristique de 5 nm, grâce à des technologies telles que FinFET.

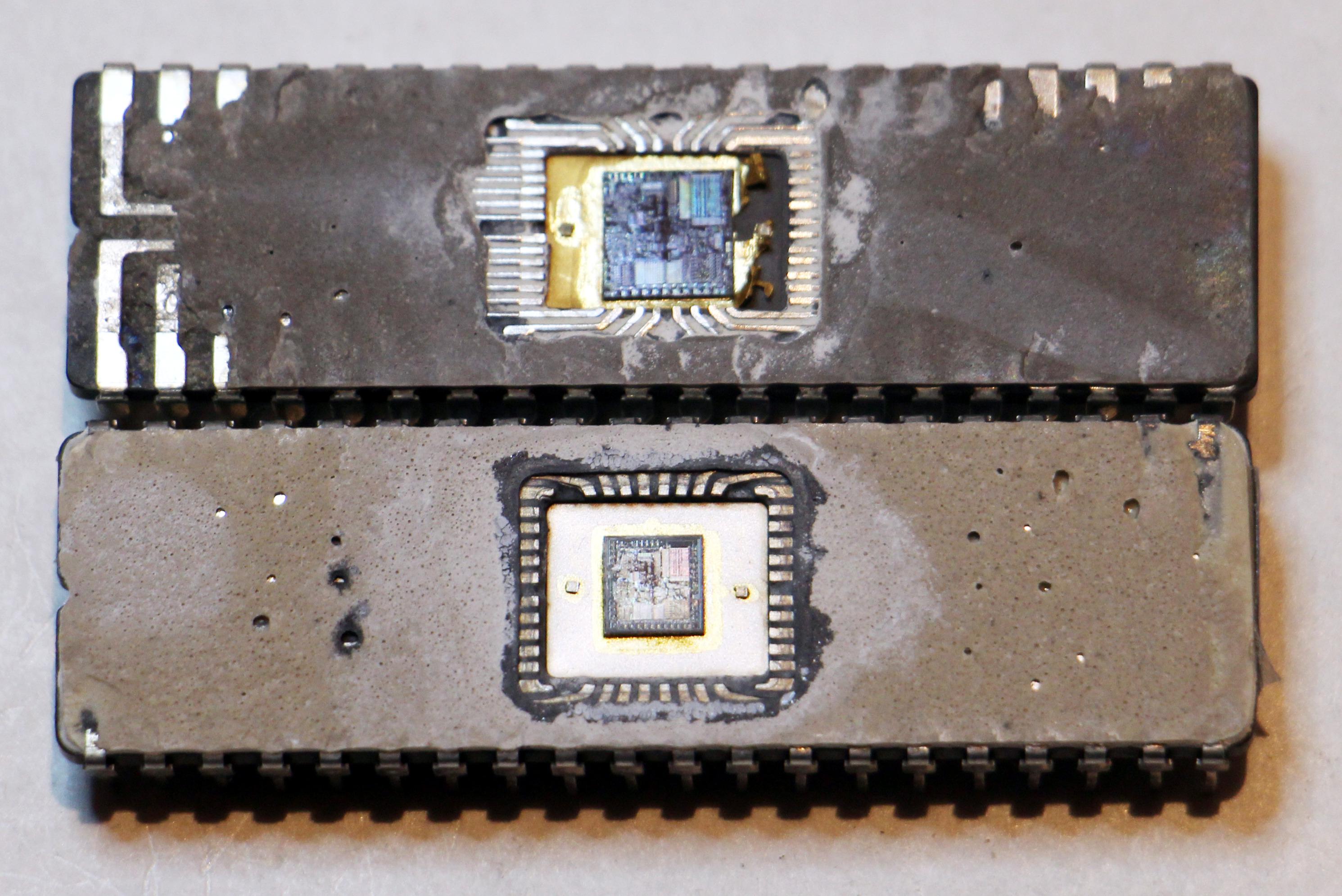

La photo ci-dessous montre la puce 8086 de 1979, ainsi que sa version avec un dé nettement plus petit de 1986. Les couvercles en céramique ont été retirés des puces pour que les cristaux soient visibles. Dans le 8086 mis à jour, les circuits internes ont été réduits de 64% en longueur par rapport à l'original, il occupe donc 40% de la surface d'origine. Le cristal lui-même n'est pas considérablement réduit; il occupe 54% de la superficie d'origine. Le boîtier du processeur n'est pas changé, le DIP 40 broches étant souvent utilisé pour les microprocesseurs.

L'ancienne puce indique 78, 79 sur le boîtier et 1979 sur le cristal, et le code de date est 7947 (47e semaine de 1979) en bas. 1978 est écrit sur le boîtier de la nouvelle puce, et 1986 est écrit sur le cristal, il n'y a pas de code de date. Par conséquent, il devrait être fabriqué en 1986 ou un peu plus tard. On ne sait pas pourquoi la nouvelle puce sur le boîtier a une date plus ancienne.

Comparaison de deux puces 8086. Le fond de la nouvelle puce a une matrice beaucoup plus petite. Le rectangle dans le coin supérieur droit est la ROM du microcode.

Le 8086 est l'une des puces les plus influentes jamais fabriquées. Cela a marqué le début de l'architecture x86 qui domine toujours les ordinateurs de bureau et serveurs. Contrairement aux processeurs CMOS modernes, le 8086 était construit sur des transistors N-MOS comme le 6502, le Z-80 et d'autres premiers processeurs. La première puce a été fabriquée en utilisant la technologie HMOS, comme Intel a appelé ce processus. En 79, Intel en a présenté une version avancée, HMOS-II, et en 82, il est passé à HMOS-III, le processus utilisé pour fabriquer le plus récent de mes deux puces. Chaque version successive de HMOS réduit la taille des composants de la puce et augmente l'efficacité.

Un MOSFET à canal N est un type spécifique de MOSFET. Leur efficacité est bien meilleure que celle de la structure MOS à canal P utilisée dans les premiers microprocesseurs tels que l'Intel 4004. Les processeurs modernes utilisent ensemble des transistors à canal N et à canal P pour réduire la consommation d'énergie - c'est ce qu'on appelle CMOS... Les vannes MOS à canal N nécessitent une résistance de rappel, qui est un transistor. Les transistors à charge d'épuisement sont un type de transistor introduit au milieu des années 1970. Les transistors de ce type sont mieux adaptés au rôle de résistances de pull-up et n'ont pas besoin de tension d'alimentation supplémentaire. Enfin, les MOSFET utilisaient à l'origine du métal pour créer des portes (la lettre M dans les MOSFET). Cependant, à la fin des années 1960, Fairchild a développé du polysilicium pour remplacer le métal. En conséquence, les puces sont plus efficaces et plus faciles à fabriquer. En conséquence, de la fin des années 1960 au milieu des années 1970, plusieurs changements radicaux se sont produits dans la production des structures MOS, conduisant au succès des 6502, Z-80, 8085, 8086 et d'autres premiers processeurs. Dans les années 80, les processeurs CMOS ont pris le relais car ils étaient plus rapides et consommaient moins d'énergie.

Curieusement, ce que signifie exactement le H de l'acronyme HMOS n'est pas tout à fait clair. Je n'ai pas trouvé de transcription de cet acronyme d'Intel. La spécification indique « le processus de fabrication de portes HMOS à canal N en silicium avancé d'Intel» ou «HMOS est un processus MOS à canal n très efficace». Intel a décrit plus tard CHMOS comme un semi-conducteur à oxyde métallique à haute vitesse complémentaire [semi-conducteur à oxyde métallique à haute vitesse complémentaire]. Motorola a identifié HMOS comme MOS haute densité. D'autres sources le décrivent comme un MOS haute vitesse ou un MOS haute densité avec des canaux courts. Intel a un brevet"Processus MOS et dispositif haute densité et haute vitesse", alors peut-être que H signifie à la fois "haute densité" et "haute vitesse".

Fait intéressant, Intel a utilisé une RAM statique 4K pour développer chacun des processus HMOS avant d'utiliser le processus pour les microprocesseurs et autres puces. Elle a utilisé une puce RAM, probablement parce qu'elle a des circuits très denses, mais elle est aussi relativement facile à concevoir, car la même cellule mémoire est répétée encore et encore. Une fois qu'elle a développé toutes les règles de configuration du circuit, elle a pu commencer à construire des processeurs beaucoup plus complexes.

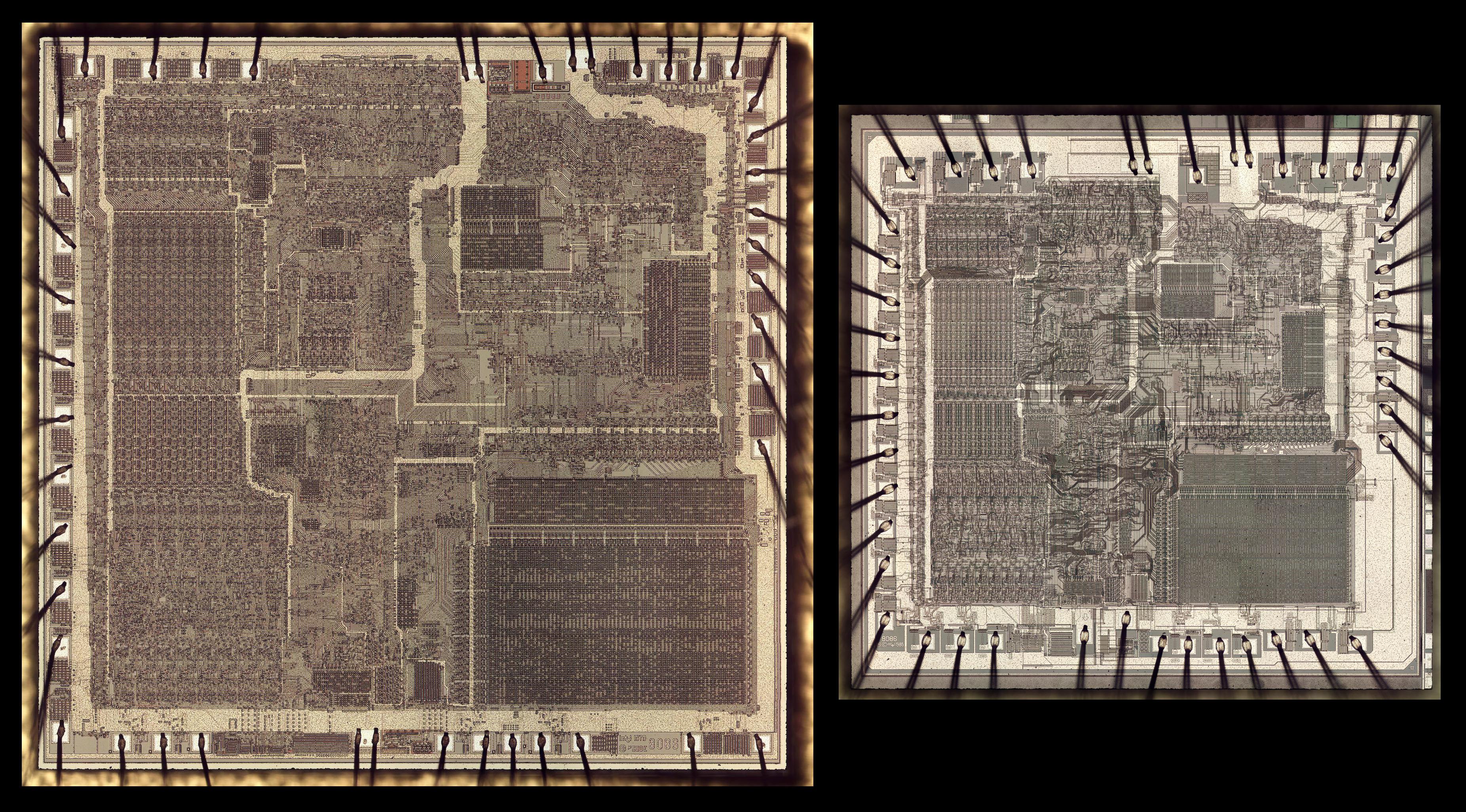

Deux versions du cristal 8086 à la même échelle. Les conducteurs entrants sont connectés aux plots situés autour du périmètre du cristal.

La photo ci-dessus montre deux versions du cristal 8086 à la même échelle. Les deux puces ont la même disposition des composants à l'intérieur, même si à première vue, elles peuvent sembler différentes. La puce de droite au milieu comporte de nombreuses lignes sombres que la puce de gauche n'a pas, mais ce n'est qu'un artefact de tournage. Ces lignes sont une couche de polysilicium située sous le métal. Sur le côté gauche du cristal, tous les conducteurs sont situés de la même manière, seulement sur la photo ils sont très pâles. Je pense que la nouvelle puce a une couche de métal plus mince, c'est pourquoi le polysilicium est mieux vu.

J'ai mis à l'échelle des photos haute résolution des deux puces pour les comparer, et il s'est avéré que les parties principales des puces sont complètement les mêmes, à l'exception de quelques différences triviales. La seule question est de savoir s'il y a eu des changements dans le microcode. De l'extérieur, ils ont l'air identiques, mais je ne les ai pas comparés petit à petit.

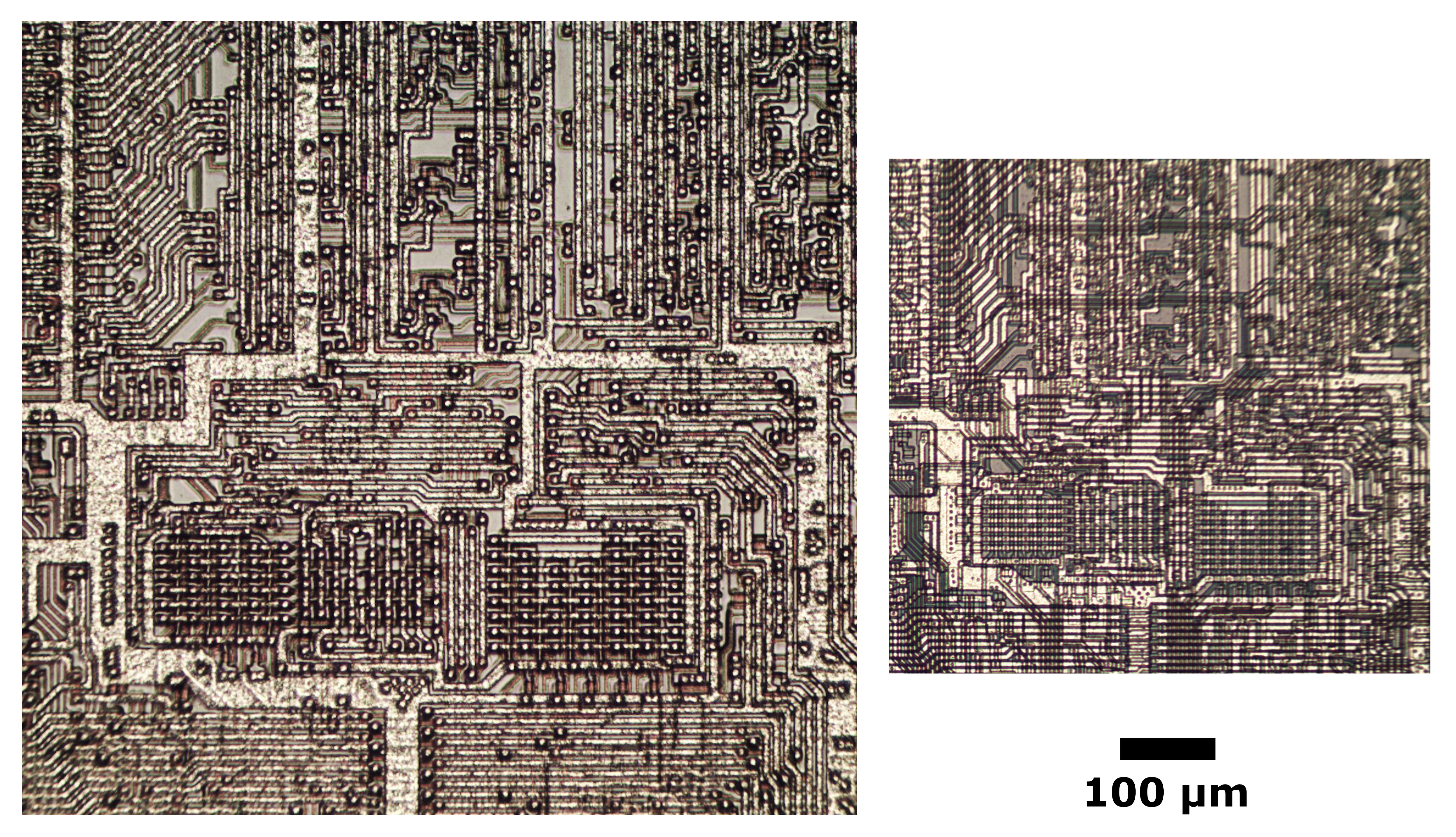

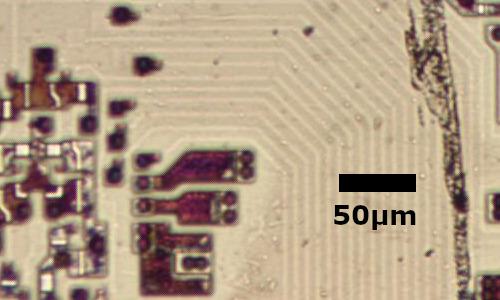

La photo agrandie ci-dessous montre les chaînes identiques de deux cristaux. Vous pouvez voir la correspondance exacte entre les composants, ce qui prouve que le circuit n'a été que réduit en taille, et non refait. Sur la photo, la couche métallique est au-dessus de la puce. La photo de droite montre du polysilicium.

Le même tracé sur deux puces différentes, à la même échelle

Mais le long du périmètre des cristaux, les différences sont importantes. Les plages de contact sont plus rapprochées, en particulier en bas à droite. Il y a deux raisons à cela. Premièrement, les plages de contact ne peuvent pas être considérablement réduites, car elles doivent être fixées avec des fils de connexion. Deuxièmement, les pistes de distribution d'énergie sont élargies sur les bords pour maintenir le courant requis. Par exemple, regardez en bas à droite de la photo, à droite de la RAM du microcode. En particulier, cela est dû au fait que les pistes de puissance au milieu du circuit sont réduites avec tout le reste, de sorte que les pistes externes doivent compenser ces pertes. De plus, la couche métallique plus mince de la nouvelle puce ne peut pas supporter le même courant à moins qu'elle ne soit expansée.

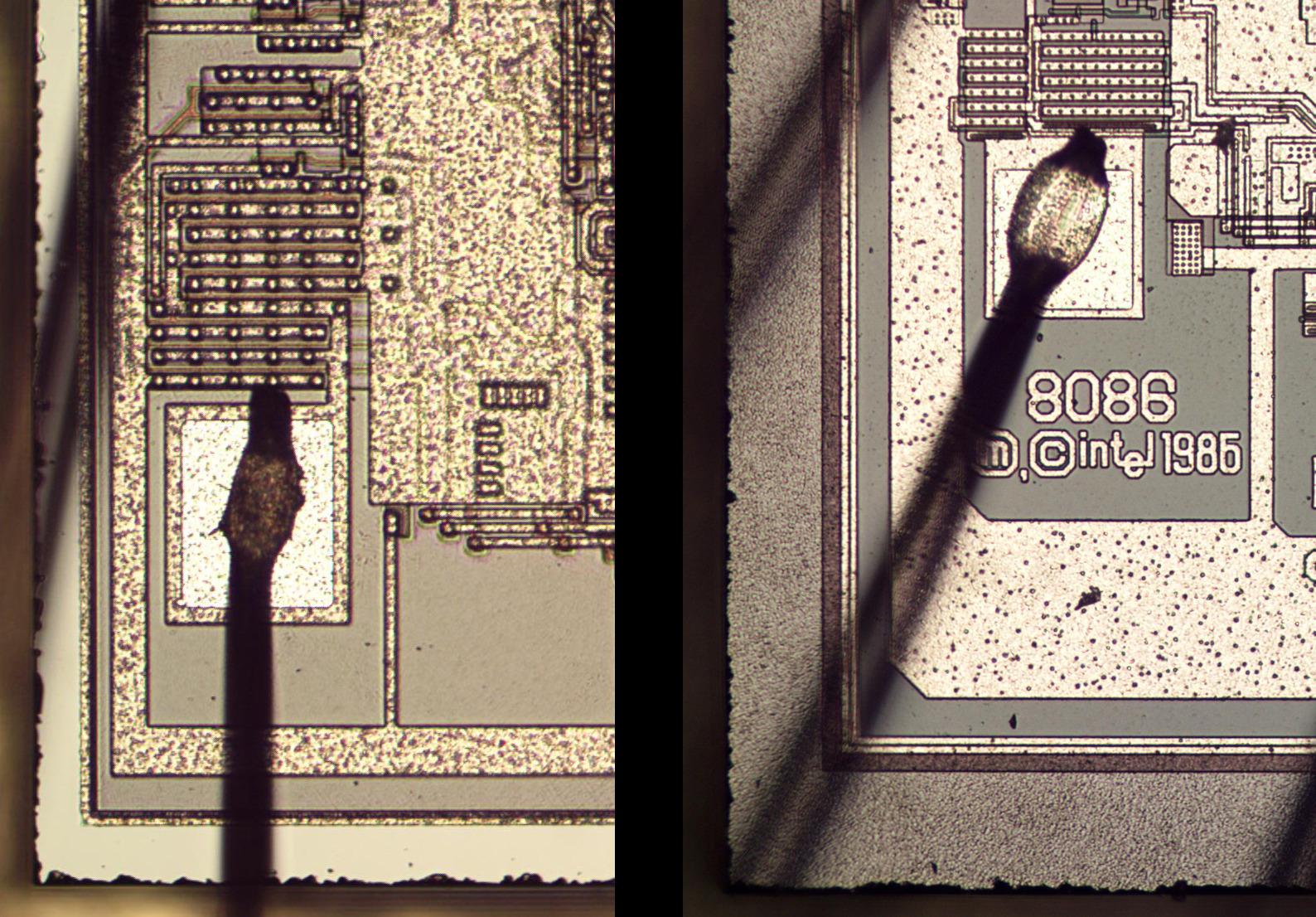

Plaque de contact et transistors associés sur l'ancienne puce (à gauche) et la nouvelle (à droite). Le chiffre "6" dans la date du copyright a un sommet inhabituellement plat - il semble qu'il soit "5" corrigé en "6".

La photo ci-dessus montre un pad avec un fil de liaison soudé. Les transistors sont situés au-dessus du plot. Le site de la nouvelle puce a presque la même taille, mais les transistors sont réduits et redessinés. Notez les conducteurs métalliques beaucoup plus épais sur la nouvelle puce. Le logo Intel a été déplacé de droite à gauche, peut-être parce qu'il y avait de l'espace libre.

Regardons de plus près les cristaux

Tout d'abord, un petit historique de la production de MOS à canal n utilisé dans le 8086 et d'autres puces de cette époque. Ces puces étaient constituées d'un substrat de silicium auquel des impuretés d'arsenic ou de bore étaient ajoutées pour former des transistors. La couche de polysilicium sur le dessus crée des grilles pour les transistors et permet de connecter des composants avec des conducteurs. Enfin, une couche métallique en haut lie tous les composants ensemble.

Le processus de fabrication de semi-conducteurs (par exemple, HMOS-III) a certaines règles pour la taille minimale et la distance entre les composants - silicium, polysilicium et couches métalliques. Si vous regardez de plus près les puces, vous verrez en quoi ces paramètres différaient pour HMOS I et HMOS III. La plaque (tirée de la technologie HMOS III) résumait les caractéristiques de divers processus HMOS. Avec chaque version, la taille caractéristique a diminué et les performances ont augmenté. En passant de HMOS-II à HMOS-III, Intel a réalisé une amélioration des performances de 40%.

| HMOS I | HMOS II | HMOS III | |

|---|---|---|---|

| Étape de diffusion (µ) | 8,0 | 6,4 | 5,0 |

| Pas de polysilicium (µ) | 7,0 | 5,6 | 4.0 |

| Pas de métal (µ) | 11,0 | 8,0 | 6,4 |

| Épaisseur de l'oxyde de valve (Å) | 700 | 400 | 250 |

| Longueur de canal (µ) | 3.0 | 2.0 | 1,5 |

| Idsat (mA) | 8,0 | 14,0 | 27,0 |

| Retard minimum de la vanne (ps) | 1000 | 400 | 200 |

| Retard de la vanne de dissipation thermique (pJ) | 1.0 | 0,5 | 0,25 |

| Taux de réduction linéaire | 1.0 | 0,8 | 0,64 |

La photo ci-dessous, prise au microscope, montre la disposition complexe des transistors dans l'ancienne puce 8086. Les zones sombres sont du silicium avec des impuretés, les rectangles clairs sont des grilles de transistor. La photo montre environ 21 transistors. La dimension clé est la longueur du canal, la longueur de la vanne de la source au drain (c'est le petit côté des rectangles lumineux). Pour ceux-ci, j'ai mesuré une longueur de 3 µm, ce qui est conforme aux spécifications publiées de HMOS I. Cela suggère que la puce a été fabriquée en utilisant le procédé 3 µm; à titre de comparaison, aujourd'hui les processeurs passent à 5 nm, ce qui est 600 fois plus petit.

Vous avez peut-être remarqué que les trois transistors de la photo ont des portes beaucoup plus grandes. Ces transistors fonctionnent comme des résistances pull-up, ce qui est typique du NMOS. Augmenter leur taille affaiblit le transistor, de sorte que le courant de rappel est faible.

8086. . – , .

La photo ci-dessous montre les transistors du 8086 plus récent à la même échelle; vous pouvez voir que les transistors sont déjà beaucoup plus petits. Les dimensions linéaires sont de 64% de l'original, donc les transistors occupent 40% de la surface par rapport aux précédents. J'ai traité ce cristal différemment, donc du polysilicium est resté dessus - ce sont des lignes jaunâtres. Le silicium avec des impuretés semble rosâtre et il est moins visible que sur la photo précédente. J'ai déterminé que la longueur de la valve était de 1,9 microns, soit 64% des 3 microns précédents. Notez que le HMOS-III maintient une longueur de canal significativement plus courte de 1,5 µm, cependant, puisque tout est réduit du même nombre de fois, la longueur de canal est plus longue que nécessaire. Cela montre qu'une diminution uniforme entraîne la perte de certains avantages du nouveau procédé, mais c'est beaucoup plus facile à faire.que de concevoir une nouvelle puce à partir de zéro.

Les transistors de la nouvelle puce 8086. Il existe de nombreux conducteurs traversants entre le silicium ou le polysilicium et la couche métallique (supprimée ici).

J'ai également étudié le pas entre les pneus sur la couche métallique. La photo ci-dessous montre les conducteurs métalliques horizontaux et verticaux de l'ancienne puce. J'ai déterminé le pas des pneus métalliques à 11 microns, ce qui coïncide avec les caractéristiques publiées de HMOS I.Réduire à 64% donne un pas de 7 microns sur la nouvelle puce, bien que le processus HMOS III supporte également 6,4 microns. Comme auparavant, le même facteur de réduction vous empêche de profiter de tous les avantages du nouveau procédé.

La couche métallique de l'ancienne puce 8086. Des conducteurs en polysilicium rougeâtre sont visibles sous le métal.

Enfin, j'ai étudié le pas des conducteurs en polysilicium. La photo ci-dessous montre l'ancien 8086; le polysilicium a été retiré et seules de faibles lignes blanches sont visibles. Ces lignes parallèles en silicium polycristallin formaient probablement un bus qui envoyait des signaux d'une partie de la puce à une autre. Pour le polysilicium, j'ai mesuré un pas de 7 microns, ce qui correspond à la documentation. Fait intéressant, en raison des propriétés du HMOS, les conducteurs en polysilicium peuvent être plus rapprochés que les conducteurs métalliques. La nouvelle puce a un pas de 4,5 microns, bien qu'il soit possible de lui donner une taille de 4 microns.

Pistes de silicium polycristallin sur l'ancienne puce 8086

Conclusions.

La mise à l'échelle du cristal permet d'augmenter la vitesse du processeur et de réduire son coût, sans perdre d'efforts pour concevoir à partir de zéro. Cependant, une comparaison des deux puces montre que la mise à l'échelle d'une matrice est plus complexe que le simple rétrécissement de la matrice entière. La majeure partie du circuit ne fait que rétrécir, mais les coussinets ne rétrécissent pas autant que le reste, ils doivent donc être réarrangés. La distribution d'énergie a également été modifiée et davantage de conducteurs d'alimentation ont été ajoutés autour de la puce.

Les microprocesseurs modernes utilisent toujours la technologie de mise à l'échelle des cristaux. En 2007, Intel est passé à un modèle tick-tock, dans lequel la mise à l'échelle des puces existantes ("tick") alterne avec la sortie d'une nouvelle microarchitecture ("tock").

Voir également: