Cependant, l'utilisation ou le débogage d'un DAC / ADC peut être difficile en raison des limitations définies par le fabricant du matériel, par exemple, sur le logiciel utilisé ou sur la façon dont le périphérique peut être contrôlé. Cela suggère de concevoir votre propre modèle d'interaction.

Dans cet article, nous examinerons la possibilité d'organiser l'interaction entre un PC et un DAC / ADC à l'aide de FPGA.

Préface

L'objectif principal de cet article est de décrire la solution à un problème spécifique, ainsi que la familiarité avec les interfaces d'interaction des circuits intégrés (CI). L'objectif principal du DAC / ADC n'est pas pris en compte ici.

Cet article nécessite une certaine connaissance de la programmation orientée objet et des circuits, donc si vous n'êtes pas familier avec ces concepts, il est recommandé de commencer par eux.

J'espère que l'expérience d'une personne qui rencontre pour la première fois le problème de la communication des appareils électroniques sera utile à quelqu'un.

Bonne chance et nouvelles réalisations à tous!

Un petit programme pédagogique sur les interfaces

Avertissement

Si vous connaissez la structure des principales interfaces utilisées pour la communication IC, vous pouvez ignorer ce point en toute sécurité.

programme éducatif

, .

, (, .) . , .

, . , , , .. , . . – , . , . , .

, .

( ), :

«-» — , . , — .

«» (, « » «») , . . , , , . .

( «») . , , , - . .

:

, . . . , .

, . , , .

(-/)

:

. .

, .

: , «» .

. .

:

. . . ( – , – , , ). « » ( ). .

, , .

() SPI I2C UART.

I2C – . I2C . I2C «-», .

, , . , . 7- 16 . , 112 . I2C (SDA) (SCL).

I2C

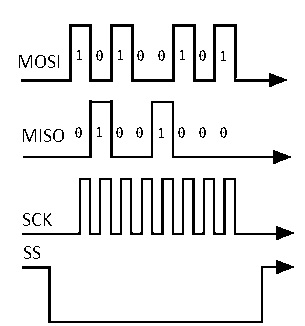

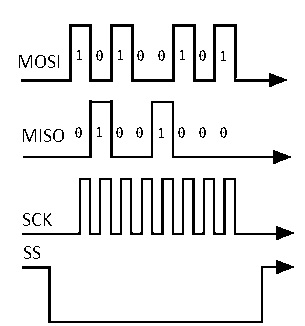

SPI – , .

SPI «-». MOSI SCLK, . MISO, . SS.

SPI

UART – – , .

RxD ( ) TxD ( ).

UART TxD . . UART , , UART , . , . 8 ( ), , .

UART «-». , UART . « » «».

UART

, .

, (, .) . , .

, . , , , .. , . . – , . , . , .

, .

( ), :

- «-»;

- «»;

- «» («»).

«-» — , . , — .

«» (, « » «») , . . , , , . .

( «») . , , , - . .

:

- ;

- ;

- -.

, . . . , .

, . , , .

(-/)

:

- ();

- ();

- ().

. .

, .

: , «» .

. .

:

- ;

- .

. . . ( – , – , , ). « » ( ). .

, , .

?

() SPI I2C UART.

I2C

I2C – . I2C . I2C «-», .

, , . , . 7- 16 . , 112 . I2C (SDA) (SCL).

I2C

SPI

SPI – , .

SPI «-». MOSI SCLK, . MISO, . SS.

SPI

UART

UART – – , .

RxD ( ) TxD ( ).

UART TxD . . UART , , UART , . , . 8 ( ), , .

UART «-». , UART . « » «».

UART

Quel est ce DAC?

Il semble que ce ne soit pas celui-ci

Tout d'abord, définissons le DAC / ADC utilisé: La

carte de débogage Analog Devices AD9993-EBZ est un périphérique qui combine quatre ADC 14 bits et deux DAC 14 bits.

Les modes de fonctionnement de ce circuit intégré sont contrôlés en modifiant l'état de ses registres internes. L'AD9993 utilise 66 registres avec une taille de mot stockée (traitée) de 8 bits, dont les adresses sont décrites par des valeurs hexadécimales à trois chiffres (12 bits de données). Deux types de commandes sont pris en charge: la commande de lecture et la commande d'écriture. En d'autres termes, afin de corriger le fonctionnement de l'IC, il est nécessaire d'envoyer une commande pour écrire une valeur de 8 bits valide à une adresse de registre spécifique. L'accès aux registres de ce circuit intégré est effectué via l'interface périphérique série (SPI), la connexion à laquelle sur la carte de mise au point est réalisée via le connecteur FIFO_0 à 40 broches ou via un groupe de contacts installé en plus.

Comme celui-ci (FIFO_0 - connecteur gris supérieur)

Exigences de base pour les paramètres de limite SPI:

- Fréquence maximale de transmission de données - 25 MHz;

- La durée des niveaux supérieur et inférieur sur la ligne de génération de signal de synchronisation est de 10 ns;

- Temps de réglage du niveau sur les lignes de transmission de données et sur la ligne de résolution - 2 ns;

- Temps de maintien de niveau sur les lignes de transmission de données et sur la ligne de résolution - 2 ns;

- Le temps de validité garanti d'un bit de données sur la ligne de transmission de l'esclave est de 2 ns.

Une description complète des fonctionnalités de l'appareil se trouve dans sa documentation .

Que dit le fabricant?

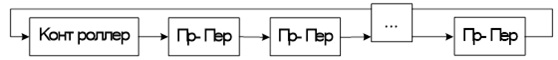

Schéma de contrôle recommandé

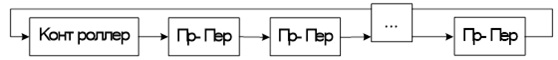

Sur la base de la documentation AD9993-EBZ, la méthode recommandée pour contrôler l'IC est d'utiliser la carte de débogage Analog Devices HSC-ADC-EVALC connectée à l'IC via un port à 40 broches et à un PC via l'interface USB.

SPIController est utilisé comme logiciel de contrôle. Circuit

recommandé

Analog Devices HSC-ADC-EVALC (basé sur Xilinx Virtex-4 FPGA)

contre:

- Prix élevé. La carte de débogage HSC-ADC-EVALC sur le site officiel d'Analog Devices est proposée pour 698,28 $.

- Interface utilisateur peu pratique. Le logiciel SPIController, en plus de la fonction principale d'écriture et de lecture de registres, ne permet pas de sauvegarder ou de programmer le démarrage des commandes.

- . SPI SPIController, . Analog Devices, SPI.

SPIController

:

- .

HSC-ADC-EVALC

Il convient de noter que l'utilisation de la carte Analog Devices HSC-ADC-EVALC comme dispositif de commande DAC / ADC n'est pas son objectif principal.

Le HSC-ADC-EVALC est principalement utilisé comme carte mémoire tampon pour l'ADC, mais il a également la fonctionnalité de configuration des cartes de débogage via SPI si les cartes connectées le prennent en charge.

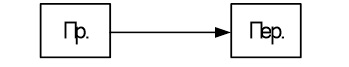

Propre modèle d'interaction

Raison d'utiliser un appareil intermédiaire

Il est évident que l'interaction entre le DAC / ADC et le PC ne peut pas être organisée directement, car le SPI, avec lequel l'AD9993-EBZ est programmé, n'est pas une interface typique d'un PC moderne.

Pour résoudre ce problème, il était nécessaire d'utiliser un périphérique intermédiaire qui convertirait les données de l'interface USB envoyées depuis l'ordinateur au format d'interface SPI pris en charge par l'IC.

Au cours de l'élaboration des options, le choix s'est porté sur l'utilisation de la carte de débogage Terasic DE10-Nano, basée sur le FPGA Cyclone V.

Propre modèle d'interaction

Pourquoi FPGA est-il cool?

Les principaux avantages de l'utilisation des FPGA:

- . DE10-Nano , , , . IDE, Verilog.

- . DE10-Nano HSC-ADC-EVALC ($110 $698.28). DE10-Nano , .

- . , .

- . FPGA- (FPGA – field-programmable gate array – , ), ( ). rocketboards c .

...

Lors de la conception du modèle d'interaction, il a été décidé d'implémenter l'interface SPI basée sur GPIO (broches à usage général), dont la base de contact est disponible sur le DE10-Nano. L'implémentation du contrôleur SPI basé sur FPGA ne devrait pas avoir créé de problèmes particuliers en raison de la grande quantité de documents sur un sujet similaire.

Cependant, la mise en œuvre de la connexion du FPGA à l'ordinateur via l'interface USB a posé des problèmes.

Le DE10-Nano possède les ports USB suivants:

- USB mini-B alimenté par la puce FT232R, réalisant une connexion UART vers USB.

- USB mini-B contrôlé par la puce SMSC USB3300, qui implémente la couche physique de l'interface USB, ainsi que pour la programmation des FPGA.

L'utilisation de ces ports est compliquée par le fait que le DE10-Nano communique avec ces ports via le soi-disant HPS ( système de processeur dur ) - une partie de la puce Cylone V qui contient un module de microprocesseur, un processeur ARM Cortex, des contrôleurs de mémoire flash et bien plus encore. La principale différence entre les HPS et les FPGA est que les HPS sont des blocs de structure invariable, optimisés pour une fonction spécifique et ne disposent pas d'outils de programmation (donc durs).

Les parties HPS et FPGA de la puce Cyclone V ont leurs propres broches. Ces broches ne sont pas librement partagées entre le HPS et le FPGA. Les contacts HPS sont configurés par un logiciel s'exécutant dans le HPS. Les broches FPGA sont programmées à l'aide d'une image de configuration FPGA via le HPS ou toute autre source externe prise en charge.

Afin d'organiser l'interaction de la logique programmable de la puce Cyclone V avec ces ports, il est nécessaire de créer un chargeur de démarrage Linux spécial fonctionnant sur le HPS, et il est également nécessaire de développer un programme capable de transférer les signaux des contrôleurs des ports USB disponibles vers les contacts libres du FPGA.

Au stade actuel des connaissances, cette question s'est avérée écrasante, il a donc été décidé de trouver une autre voie. Cependant, pour les personnes confrontées à un problème similaire et ayant décidé de le résoudre, il peut être utile de lire un article sur une solution possible.

Il y a une sortie!

Après avoir soigneusement parcouru Internet, il a été décidé d'utiliser un contrôleur UART externe.

Le contrôleur UART externe est une petite carte basée sur la puce FT232RL. La carte possède des connecteurs miniUSB-B pour la communication avec un ordinateur et un connecteur à 6 broches pour la communication avec des microcontrôleurs et des appareils.

Le contrôleur est connecté via l'interface USB au PC et via la base de contact GPIO au DE10-Nano.

Le contrôleur lui-même de Waveshare (utilisé dans le projet)

L'utilisation d'une interface UART via USB pour transférer des données à partir d'un PC élimine pratiquement le besoin de gérer le périphérique de protocole USB complexe et multicouche. Désormais, l'interaction via l'interface USB n'est plus notre préoccupation, puisque cette tâche est attribuée aux pilotes préinstallés dans le système ou installés indépendamment par l'utilisateur.

En plus des lignes d'alimentation et de masse, ainsi que des lignes de transmission et de réception de données, il y a des broches sur la carte, signées RTS et CTS. Ces contacts sont utilisés pour ce que l'on appelle le contrôle de flux - un mécanisme conçu pour signaler la disponibilité à recevoir des données du dispositif maître ou esclave, en fonction de l'état des lignes. L'utilisation de ces lignes n'est pas nécessaire, par conséquent, pour désactiver le mécanisme, il est nécessaire d'indiquer dans les paramètres du pilote de l'ordinateur que le contrôle de flux n'est pas utilisé (il s'agit généralement de la configuration par défaut).

Lorsqu'il est connecté à un PC Windows, le contrôleur UART est détecté comme un port série virtuel. Par conséquent, le développement d'un schéma d'interaction avec un PC revient à créer un logiciel avec la fonctionnalité d'interagir avec un port virtuel série, ainsi qu'à développer un projet pour un FPGA qui implémente la réception / transmission de données via l'interface UART.

Le contrôleur UART externe est en fait un analogue absolu du contrôleur déjà présent sur le DE10-Nano, mais son seul avantage est la possibilité de se connecter directement à des broches FPGA libres. Le coût d'un tel appareil varie de 5 $ à 10 $.

Développement de logiciels

informations générales

Comme déjà mentionné, le développement de logiciels pour un PC se réduit à la création d'un programme prenant en charge l'échange d'informations avec un port série virtuel. Lors de l'analyse des outils logiciels disponibles pour le développement logiciel, le choix s'est porté sur le langage de programmation Java 8ème édition utilisant la bibliothèque RTXT.

Java est un langage de programmation orienté objet fortement typé avec un certain nombre de fonctionnalités clés. En particulier, les programmes écrits dans le langage de programmation Java sont traduits en un bytecode spécial, qui leur permet de fonctionner sur toute architecture informatique pour laquelle il existe une implémentation d'une machine virtuelle Java.

Les bibliothèques standard Java n'ont pas la capacité de communiquer avec un port série virtuel. C'est à cela que sert la bibliothèque RTXT. RTXT est distribué sous une licence de logiciel libre. La bibliothèque utilise l'implémentation système de l'interaction avec les interfaces et fournit des classes pour les opérations d'analyse, de connexion, de lecture et d'écriture à l'aide du port série. Pour en savoir plus sur cette bibliothèque, cliquez ici .

L'ancienne mais fiable bibliothèque intégrée Swing est utilisée comme un outil pour développer l'interface utilisateur. En raison de la possibilité de changer de thème, une interface utilisateur simple dans Swing peut ne pas paraître

Le programme lui-même est spartiate simple et utilise principalement les capacités documentées de la bibliothèque RTXT.

La fonctionnalité principale du programme

Voici comment les ports disponibles sont déterminés:

public String[] getPorts() {

ports = CommPortIdentifier.getPortIdentifiers();

while (ports.hasMoreElements()) {

CommPortIdentifier curPort = (CommPortIdentifier) ports.nextElement();

if (curPort.getPortType() == CommPortIdentifier.PORT_SERIAL) {

portMap.put(curPort.getName(), curPort);

}

}

return portMap.keySet().toArray(new String[0]);

}

Connexion au port sélectionné:

public void connect() {

String selectedPort = (String)gui.ports.getSelectedItem();

selectedPortIdentifier = portMap.get(selectedPort);

CommPort commPort;

try{

commPort = selectedPortIdentifier.open("UART controller", TIMEOUT);

serialPort = (SerialPort)commPort;

serialPort.setSerialPortParams(BAUD_RATE, SerialPort.DATABITS_8, SerialPort.STOPBITS_1, SerialPort.PARITY_NONE);

gui.writeLog(selectedPort + " opened successfully.");

}catch (PortInUseException e){

gui.writeLogWithWarning(selectedPort + " is in use. (" + e.toString() + ")");

}catch (Exception e){

gui.writeLogWithWarning("Failed to open " + selectedPort + " (" + e.toString() + ")");

}

}

Processus de transfert de données:

public boolean writeData(byte[] bytes){

boolean successfull = false;

try {

gui.writeLog("WRITING: " + HexBinUtil.stringFromByteArray(bytes));

output.write(bytes);

output.flush();

successfull = true;

}

catch (Exception e) {

gui.writeLogWithWarning("Failed to write data. (" + e.toString() + ")");

}

return successfull;

}

Réception de données:

public void serialEvent(SerialPortEvent serialPortEvent) {

if (serialPortEvent.getEventType() == SerialPortEvent.DATA_AVAILABLE) {

try {

byte singleData = (byte)input.read();

gui.writeLog("READING: " + HexBinUtil.stringFromByteArray(singleData));

}

catch (Exception e) {

gui.writeLogWithWarning("Failed to read data. (" + e.toString() + ")");

}

}

}

Comme déjà mentionné, le DAC / ADC est contrôlé en transmettant la commande d'écriture d'une valeur de 8 bits valide à une adresse de registre spécifique décrite dans la documentation. Pour déterminer l'état actuel du registre, vous devez envoyer la commande de lecture et spécifier l'adresse du registre demandé. Description complète comme toujours dans la documentation .

Transmission de données UART

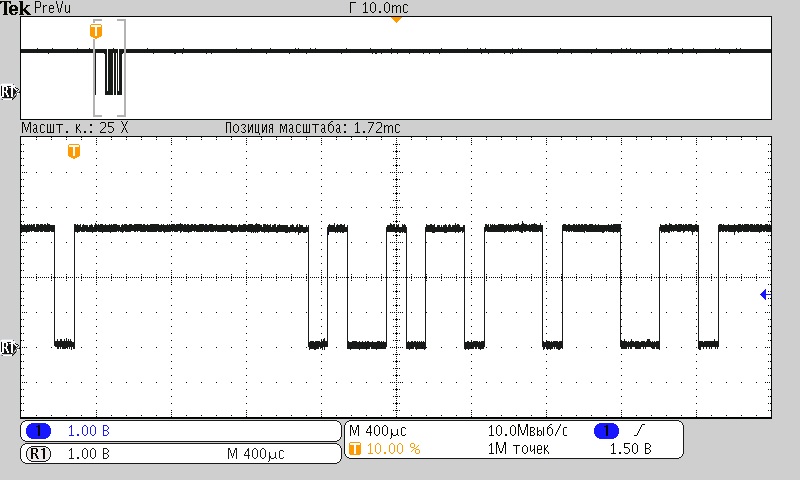

Au cours de l'étude de l'AD9993-EBZ, il a été constaté que seuls 8 bits de données sont utilisés dans l'espace d'adressage de registre de 12 bits disponible. De plus, la valeur transmise de l'état du registre est décrite par 8 bits. Pour déterminer le type de transfert de données (écriture / lecture), il est nécessaire de transférer 1 bit de données.

Étant donné que la limitation actuelle de la taille maximale d'un message sur l'interface UART est de 8 bits de données, il a été décidé de transmettre 3 messages consécutifs de 8 bits pendant le processus d'écriture et 2 messages pendant le processus de lecture.

Le premier colis contiendra le type de transmission de données, dupliqué pour toute la taille du colis. Par conséquent, il ne peut y avoir que deux valeurs possibles: 00000000 pour la lecture et 11111111 pour l'écriture, respectivement. L'utilisation d'une salve entière pour la transmission d'un bit de données a été faite pour simplifier le traitement ultérieur des signaux reçus.

Ensuite, l'adresse du registre demandé et la valeur transmise de l'état du registre pendant le processus d'enregistrement sont transmises.

Oscillogramme du package UART développé

Interface utilisateur

Les principaux éléments de l'interface utilisateur du logiciel sont des boutons de connexion / déconnexion des ports série disponibles (éléments 3, 4), des champs pour saisir l'adresse et les valeurs de registre (éléments 7, 8), une fenêtre de journal (élément 6). Le logiciel est conçu pour interagir avec lui dans deux états: «connecté au port» et «déconnecté du port». Les états déterminent l'activité de certains éléments sur l'interface du programme et limitent également l'exécution de certaines méthodes afin de réduire la probabilité d'erreurs et d'utilisation incorrecte du logiciel. Lorsqu'il est activé, le programme est dans l'état «déconnecté du port». De plus, afin de faciliter le travail avec le programme (dont j'étais l'un des principaux objectifs du projet), la fonctionnalité de connexion de fichiers avec des commandes déjà enregistrées au format JSON a été ajoutée (élément 10).

Processus de chargement des commandes:

Sélection de fichiers

Interface de commandes La

fonctionnalité vous permet de trier les commandes chargées en sections (élément 12), de personnaliser le processus de travail avec les commandes connectées (s'il faut envoyer une commande au port série immédiatement lorsque vous appuyez dessus, ou remplir les champs d'adresse et de valeur conformément à la commande sélectionnée) ...

Développement d'un projet pour FPGA

informations générales

Avant de commencer à développer un projet pour un FPGA, vous devez décider de la tâche qu'il doit résoudre.

Cela ressemble à ceci: le projet pour le FPGA doit prendre en charge la conversion de données suivante:

Diagramme de conversion de données

L'entrée DE10-Nano reçoit les signaux de la ligne Tx de l'interface UART (signal supérieur). Ensuite, le FPGA doit déterminer correctement les données reçues à partir de trois messages de 8 bits chacun et les convertir au format de message SPI correspondant à la documentation (présenté en 4 lignes).

Les principaux modules requis pour mettre en œuvre cette conversion sont un module contrôleur UART et un module contrôleur SPI. C'est à eux que revient le reste du chapitre.

Lors du développement de projets pour FPGA, la 17e version de l'IDE Qartus Prime Lite Edition a été utilisée.

Si vous n'avez aucune expérience avec Quartus ou n'avez pas du tout programmé de FPGA, il est recommandé de commencer par un exemple clair (à mon avis) du premier projet sur Quartus.

Je tiens à noter que tous les extraits du code Verilog décrits ci-dessous sont une compilation de solutions trouvées sur Internet, qui ne prétendent être aucune originalité. Là encore, l'objectif principal de ce projet est de résoudre un problème spécifique.

Contrôleur UART

La description

Le contrôleur UART se compose de trois modules:

- un générateur de pulsion;

- module d'enregistrement;

- module de lecture.

Il est recommandé de consulter cet article , dont la plupart des informations ont été tirées. De plus, je me concentrerai uniquement sur les détails de mise en œuvre les plus importants (à mon avis).

Un générateur de pulsion

L'interface UART étant asynchrone, le récepteur doit générer son propre signal de référence pour recevoir correctement le signal émis, ce qui lui permet de déterminer correctement le début d'un nouveau bit d'information.

Il existe une gamme généralement acceptée de débits en bauds UART standard: 300; 600; 1200; 2400; 4800; 9600; 19200; 38400; 57600; 115200; 230400; 460800; 921600 bauds Dans notre cas, le transfert de données s'effectue à 9600 bauds. Ensuite, nous devons obtenir un générateur avec une fréquence 16 fois supérieure au débit de symboles. Ceci est nécessaire pour détecter correctement le niveau du signal transmis.

Pour générer des impulsions, un générateur de 50 MHz est utilisé sur la puce. Pour obtenir la fréquence souhaitée, il est nécessaire de prendre en compte toutes les 325ème impulsions du générateur.

Voici à quoi cela ressemblera dans Verilog:

input Clk; // 50

input Rst_n; //

input [15:0] BaudRate; // , 325

output Tick; //

reg [15:0] baudRateReg; //

always @(posedge Clk or negedge Rst_n)

if (!Rst_n) baudRateReg <= 16'b1;

else if (Tick) baudRateReg <= 16'b1;

else baudRateReg <= baudRateReg + 1'b1;

assign Tick = (baudRateReg == BaudRate);

endmodule

Module lecteur

Le lecteur convertit le signal d'entrée de la ligne RX en un tableau de données de sortie 8 bits.

Lecture directe et transfert des données lues vers la sortie:

input Clk, Rx,Tick; // 50, Rx,

input [3:0]NBits; // , 8

output RxDone; //

output [7:0]RxData; //

reg read_enable = 1'b0; //

reg RxDone = 1'b0; //

reg [3:0] counter = 4'b0000; //

reg start_bit = 1'b1; //

reg [4:0]Bit = 5'b00000; //

reg [7:0] RxData; //

reg [7:0] Read_data= 8'b00000000; //

always @ (posedge Tick) //

begin

if (read_enable)

begin

RxDone <= 1'b0; //

counter <= counter+1'b1; //

if ((counter == 4'b1000) & (start_bit)) //

begin

start_bit <= 1'b0;

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (!start_bit) & (Bit < NBits)) //

begin

Bit <= Bit+1'b1;

Read_data <= {Rx,Read_data[7:1]};

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (Bit == NBits) & (Rx)) //

begin

Bit <= 4'b0000;

RxDone <= 1'b1; //

counter <= 4'b0000; //

start_bit <= 1'b1; //

end

end

end

always @ (posedge Clk)

begin

if (NBits == 4'b1000) // 8 ,

begin

RxData[7:0] <= Read_data[7:0];

end

end

Module de transmission

Le module de transmission convertit le signal d'entrée 8 bits en un paquet de données série UART.

Transfert de données direct:

input Clk, Rst_n, TxEn; // 50, ,

input Tick; //

input [3:0]NBits; //

input [7:0]TxData;

output Tx;

output TxDone;

reg Tx;

reg TxDone = 1'b0;

reg write_enable = 1'b0;

reg start_bit = 1'b1;

reg stop_bit = 1'b0;

reg [4:0] Bit = 5'b00000;

reg [3:0] counter = 4'b0000;

reg [7:0] in_data=8'b00000000;

always @ (posedge Tick) //

begin

if (!write_enable)

begin

TxDone = 1'b0;

start_bit <=1'b1;

stop_bit <= 1'b0;

end

if (write_enable)

begin

counter <= counter+1'b1; //

if(start_bit & !stop_bit)//

begin

Tx <=1'b0;

in_data <= TxData;

if ((counter == 4'b1111) & (start_bit) ) //

begin

start_bit <= 1'b0;

in_data <= {1'b0,in_data[7:1]};

Tx <= in_data[0];

end

if ((counter == 4'b1111) & (!start_bit) & (Bit < NBits-1)) //

begin

in_data <= {1'b0,in_data[7:1]};

Bit<=Bit+1'b1;

Tx <= in_data[0];

start_bit <= 1'b0;

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (Bit == NBits-1) & (!stop_bit)) //

begin

Tx <= 1'b1;

counter <= 4'b0000;

stop_bit<=1'b1;

end

if ((counter == 4'b1111) & (Bit == NBits-1) & (stop_bit) ) //

begin

Bit <= 4'b0000;

TxDone <= 1'b1;

counter <= 4'b0000;

//start_bit <=1'b1;

end

end

end

Contrôleur SPI

Digression importante

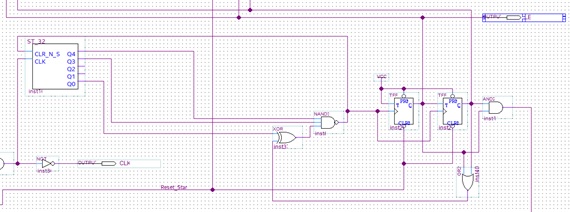

Etant donné que le contrôleur SPI, implémenté sur la base d'un FPGA, est une structure logique plus complexe que le contrôleur UART, l'explication supplémentaire de la logique de fonctionnement est plus facile à réaliser sur le modèle de circuit du contrôleur.

Schéma général du contrôleur

Le modèle développé peut être divisé en 3 modules principaux:

- module d'écriture séquentielle;

- module de compteur de bits;

- module d'analyse d'erreurs.

La division en modules est plutôt arbitraire, car le circuit présente une connectivité élevée entre les éléments utilisés. La division est basée sur les tâches effectuées par des groupes d'éléments individuels, présentées dans le schéma général.

Le cadencement du circuit est assuré par un signal de 12,5 MHz fourni via la ligne CLK_125.

Le début du travail du contrôleur sur la formation d'un message de contrôle est effectué par le signal "START". Par ce signal, tous les modules du circuit sont mis à leur état initial et le début du cycle de formation des signaux requis sur les lignes de sortie CLK, SS, MOSI de l'interface SPI est initialisé

Module d'écriture séquentielle

Le module d'écriture série effectuera la tâche principale du contrôleur SPI, à savoir la sortie de données de bits parallèles vers la ligne MOSI série. Ceci est dû à l'élément RG_24_PI_SO, qui fonctionne sur le principe d'un registre à décalage basé sur des bascules D.

L'élément RG_24_PI_SO dispose de 24 entrées de données correspondant à la documentation AD9993-EBZ sur le format d'envoi SPI. Ils incluent:

- Données de commande (DATA_0 - DATA_7);

- Enregistrer les données d'adresse (ADR_0 - ADR_12);

- Bit de mode écriture / lecture W / R.

Les signaux présentés sont écrits en parallèle à un niveau logique "1" sur l'entrée LoadP_ShiftN. En outre, au niveau logique «0» à l'entrée LoadP_ShiftN, à chaque cycle d'horloge à l'entrée CLK, l'élément reproduit alternativement les données enregistrées sur la ligne série de la sortie MOSI.

Module compteur de bits

Le module compteur de bits doit déterminer la durée du signal de validation d'écriture de données sur la ligne SS de l'interface SPI. Etant donné que, selon la documentation AD9993-EBZ, la durée du signal de validation doit être égale à la durée totale des données transmises, il devient nécessaire de compter 24 impulsions de synchronisation à partir du début de la transmission des données pour déterminer la durée requise du signal de validation. La fonction de comptage est effectuée par l'élément ST_32, qui, lorsque le 24e signal d'horloge est détecté, reproduit un signal qui est utilisé pour remettre à zéro le compteur, ainsi que pour terminer le signal de validation transmis.

En plus de la fonctionnalité principale, le module compteur de bits est également chargé d'initialiser le processus d'analyse des erreurs, dont l'action initiale est d'envoyer la commande de lecture de valeur à l'adresse du dernier registre enregistré. Étant donné que le processus d'analyse des erreurs doit être lancé après un intervalle de temps équivalent à la durée de 23 impulsions de synchronisation à partir du moment où le dernier bit de données transmis a été transmis (établi expérimentalement), le compteur de bits après le signal de réinitialisation passe au mode de comptage à 23 impulsions de synchronisation, ce qui garantit le fonctionnement du processus d'analyse des erreurs.

Module d'analyse des erreurs

Comme mentionné dans l'explication du module précédent, pour fournir la fonctionnalité d'analyse d'erreur, un procédé a été développé sur la base de la lecture de la valeur de la commande stockée sur le circuit intégré à l'adresse de registre utilisée dans le processus d'enregistrement de données. Le processus de lecture est nécessaire pour comparer la valeur écrite avec les données lues pour identifier les incohérences, et donc pour déterminer l'erreur qui s'est produite. Le module d'analyse d'erreur est basé sur l'élément RG_8_SI_PO, qui fonctionne sur le principe d'un registre à décalage. L'élément convertit les signaux reçus via le port série MISO en une sortie parallèle 8 bits. Ensuite, les données sont comparées à la valeur de la commande utilisée pendant le processus d'enregistrement des données. La fonctionnalité de comparaison est effectuée par l'élément CMP_8 sur la base de la logique ou exclusif. Si un écart est trouvé,le module envoie un signal à la sortie LED, qui sera dans l'état d'une unité logique jusqu'au prochain processus d'enregistrement de données. On suppose que la sortie LED sera connectée à l'une des LED, dont un groupe est présent sur la carte de développement DE10 Nano, ce qui signalera visuellement une erreur qui s'est produite.

Conclusion

Suite à la résolution de ce problème, un schéma d'interaction entre un PC et un dispositif DAC / ADC a été conçu et mis en œuvre physiquement avec un certain nombre d'avantages clés. Lors de la mise en œuvre, le problème de connexion du FPGA et du PC a été résolu. La solution à cela était d'utiliser un module UART externe. Le logiciel du PC a été écrit en langage Java. Le logiciel dispose d'une interface avec des capacités de base pour la transmission et la réception de données dans le format d'envoi UART développé, en outre, il a la fonction de charger des commandes enregistrées. Des contrôleurs UART et SPI basés sur FPGA ont été développés.

Les enjeux envisagés dans le cadre de ce projet permettent:

- évaluer les modes d'interaction des circuits intégrés avec des dispositifs externes;

- évaluer les moyens d'utiliser les FPGA comme dispositif de correspondance, un tampon pour l'échange de données;

- explorer l'une des approches les plus efficaces pour développer des logiciels pour une utilisation pratique.

PS Je serai heureux de tous les ajouts, remarques et indications d'erreurs.